Презентация ОТМП. Элементы и узлы ЭВМ. (Тема 2) онлайн

На нашем сайте вы можете скачать и просмотреть онлайн доклад-презентацию на тему ОТМП. Элементы и узлы ЭВМ. (Тема 2) абсолютно бесплатно. Урок-презентация на эту тему содержит всего 63 слайда. Все материалы созданы в программе PowerPoint и имеют формат ppt или же pptx. Материалы и темы для презентаций взяты из открытых источников и загружены их авторами, за качество и достоверность информации в них администрация сайта не отвечает, все права принадлежат их создателям. Если вы нашли то, что искали, отблагодарите авторов - поделитесь ссылкой в социальных сетях, а наш сайт добавьте в закладки.

Презентации » Технология » ОТМП. Элементы и узлы ЭВМ. (Тема 2)

Оцените!

Оцените презентацию от 1 до 5 баллов!

- Тип файла:ppt / pptx (powerpoint)

- Всего слайдов:63 слайда

- Для класса:1,2,3,4,5,6,7,8,9,10,11

- Размер файла:2.91 MB

- Просмотров:168

- Скачиваний:3

- Автор:неизвестен

Слайды и текст к этой презентации:

№4 слайд

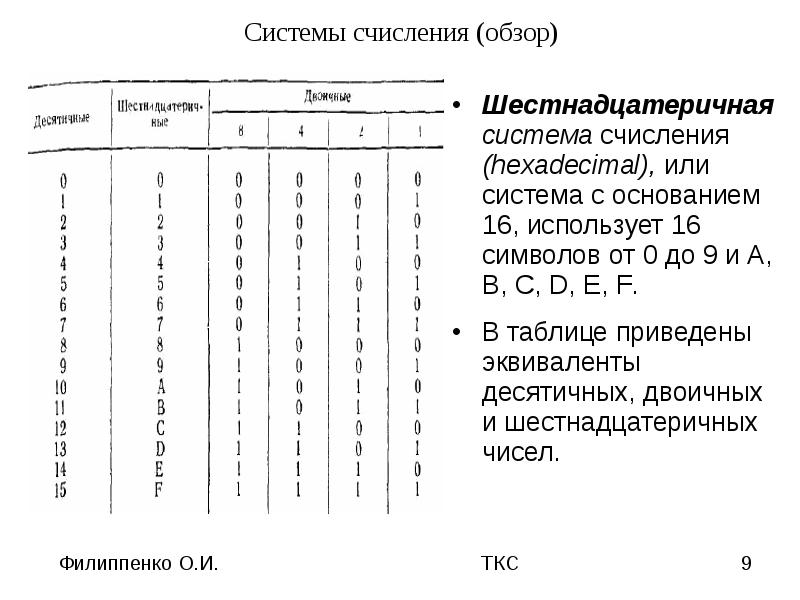

Содержание слайда: Системы счисления (обзор)

Способ записи чисел знаками называется системой счисления. Системы счисления делятся на непозиционные, например, римская система счисления, и позиционные.

В непозиционных системах значение конкретной цифры постоянно и не зависит от ее расположения в записи числа. Примером такой системы счисления является Римская система записи числа. Например, в числе XXXVII значение цифры X не зависит от ее местоположения в записи числа. Оно везде равно 10.

Система называется позиционной, если значение каждой цифры, входящей в запись числа, определяется ее местоположением в числе.

В цифровой технике нашла применение только позиционная система счисления.

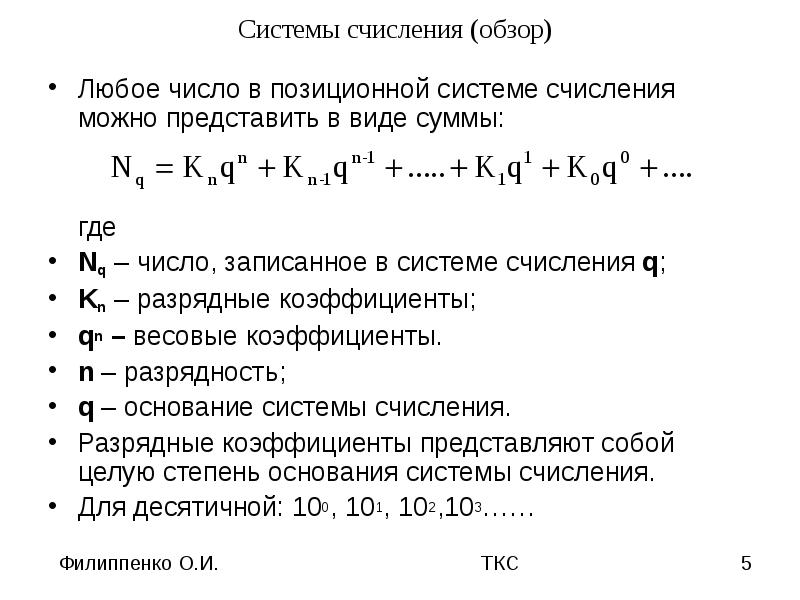

№5 слайд

Содержание слайда: Системы счисления (обзор)

Любое число в позиционной системе счисления можно представить в виде суммы:

где

Nq – число, записанное в системе счисления q;

Kn – разрядные коэффициенты;

qn – весовые коэффициенты.

n – разрядность;

q – основание системы счисления.

Разрядные коэффициенты представляют собой целую степень основания системы счисления.

Для десятичной: 100, 101, 102,103……

№6 слайд

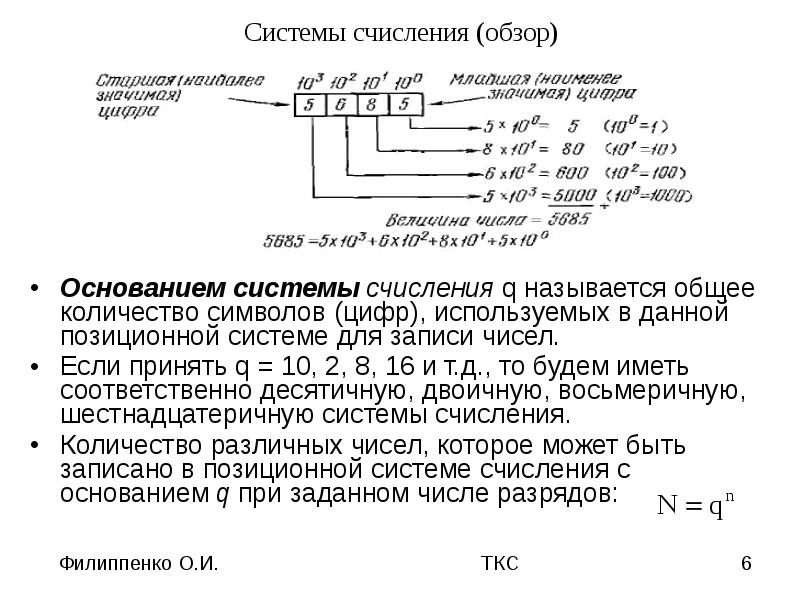

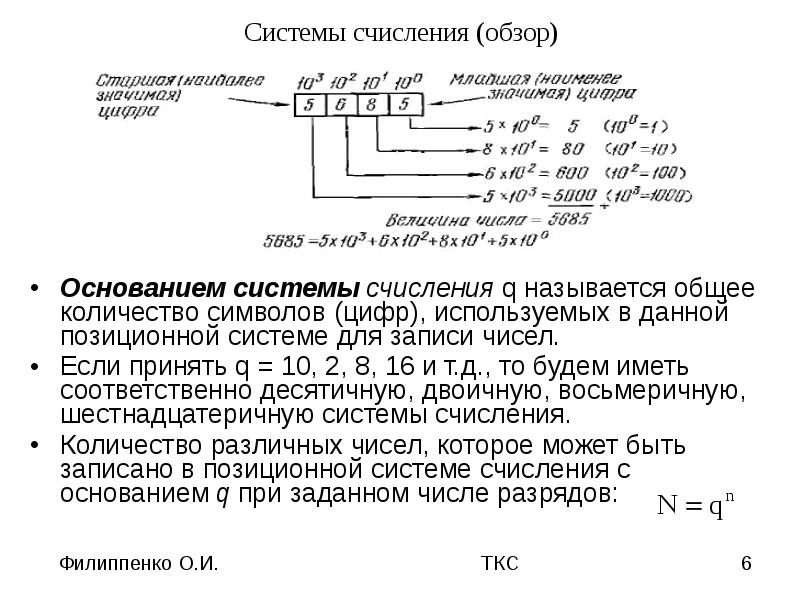

Содержание слайда: Системы счисления (обзор)

Основанием системы счисления q называется общее количество символов (цифр), используемых в данной позиционной системе для записи чисел.

Если принять q = 10, 2, 8, 16 и т.д., то будем иметь соответственно десятичную, двоичную, восьмеричную, шестнадцатеричную системы счисления.

Количество различных чисел, которое может быть записано в позиционной системе счисления с основанием q при заданном числе разрядов:

№7 слайд

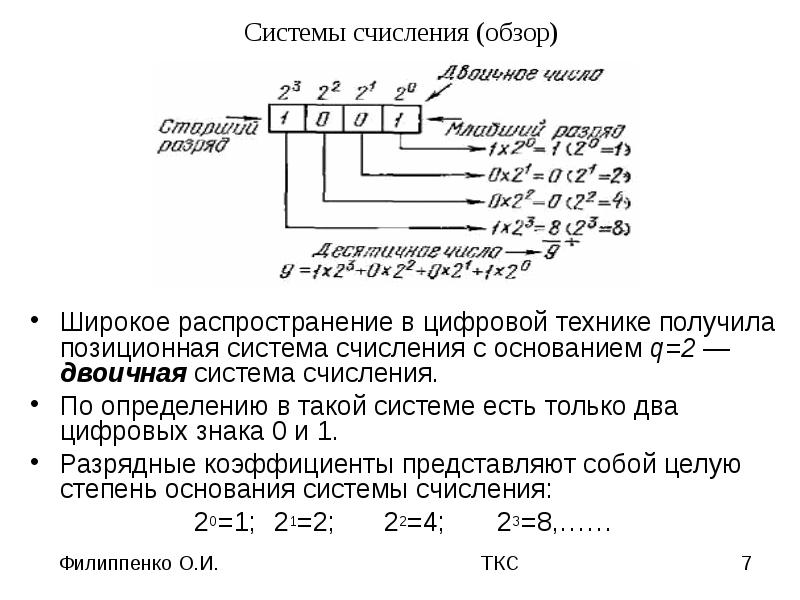

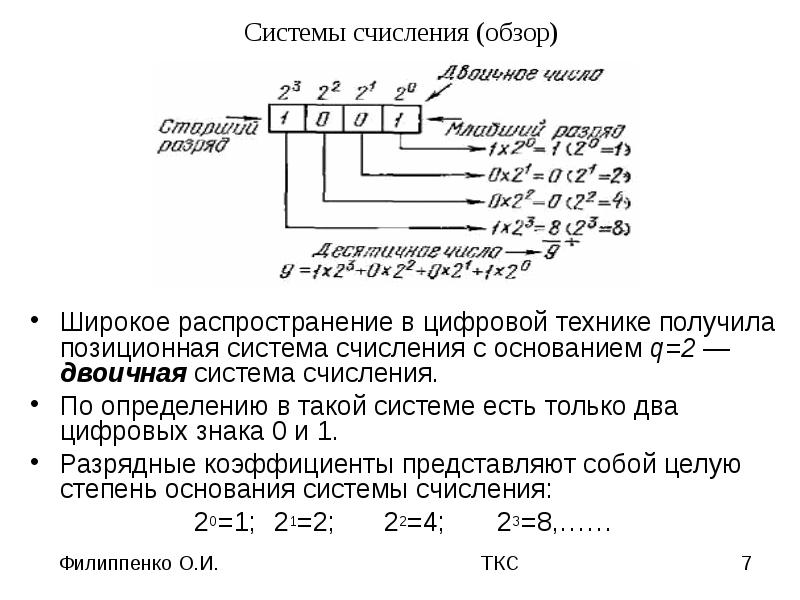

Содержание слайда: Системы счисления (обзор)

Широкое распространение в цифровой технике получила позиционная система счисления с основанием q=2 — двоичная система счисления.

По определению в такой системе есть только два цифровых знака 0 и 1.

Разрядные коэффициенты представляют собой целую степень основания системы счисления:

20=1; 21=2; 22=4; 23=8,……

№10 слайд

Содержание слайда: Системы счисления (обзор)

Над числами в двоичной системе счисления могут выполняться арифметические и логические операции.

К арифметическим относятся четыре операции: сложение, вычитание, умножение и деление. Алгоритм выполнения арифметических операций такой же, как и в десятичной системе счисления.

Логические операции относятся к поразрядным (операции выполняются внутри каждого разряда без переносов и заемов).

№11 слайд

Содержание слайда: Логические устройства

Последовательным называется устройство, в котором входные переменные подаются на вход и выходные переменные снимаются с выхода не одновременно, а последовательно.

Параллельным называется устройство, в котором все разряды входных переменных подаются на вход и все разряды выходных переменных снимаются с выхода одновременно.

В последовательно - параллельных устройствах входные и выходные переменные представлены в различных формах. Либо на вход переменные подаются последовательно, а с выхода они снимаются одновременно, либо наоборот.

По принципу действия все логические устройства делятся на два класса комбинационные устройства и цифровые автоматы.

Комбинационными устройствами или автоматами без памяти называют логические устройства выходные сигналы которых однозначно определяются только действующей в настоящий момент на входе комбинацией переменных и не зависят от значений переменных действовавших на входе ранее.

Цифровыми автоматами или автоматами с памятью называют логические устройства выходные сигналы которых определяются не только действующей в настоящий момент на входе комбинацией переменных, но и всей последовательностью входных переменных действовавших в предыдущие моменты времени.

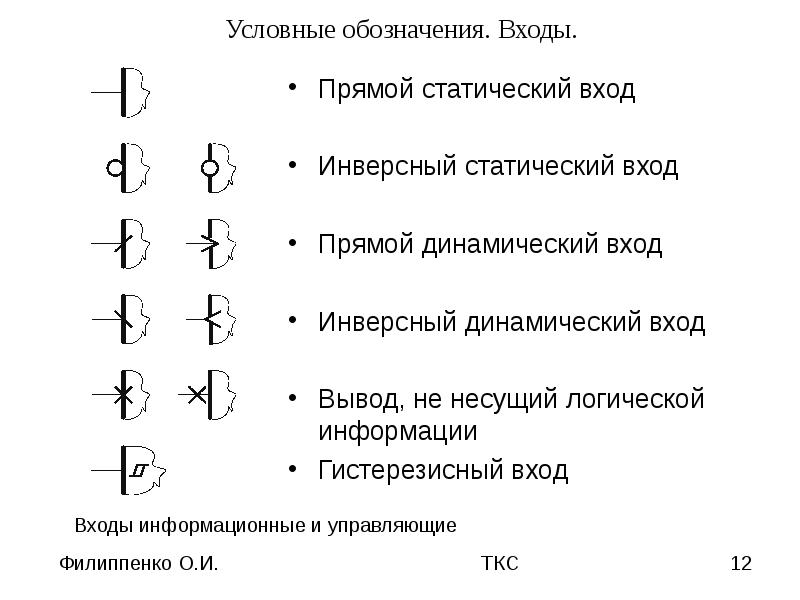

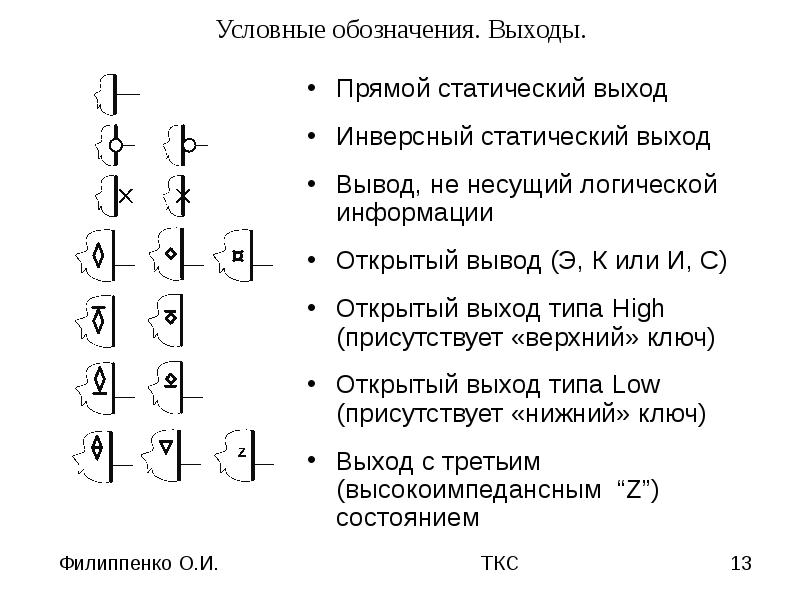

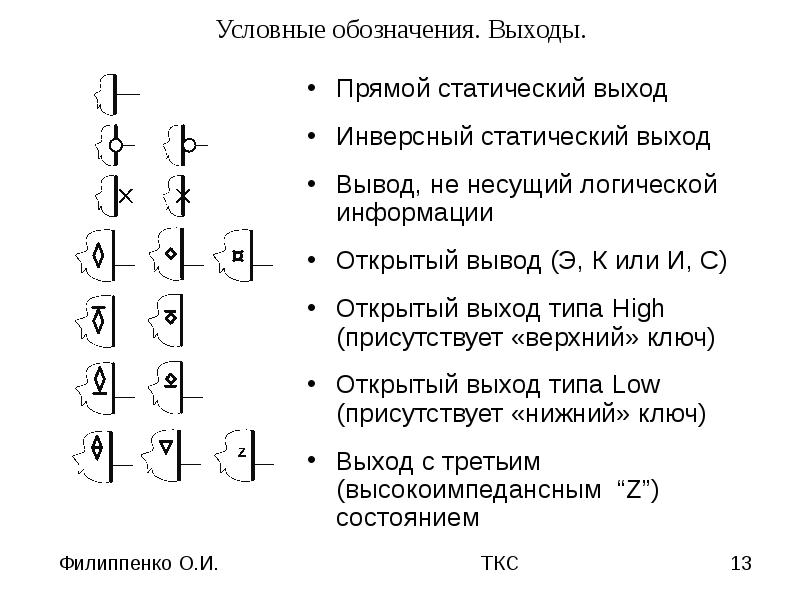

№13 слайд

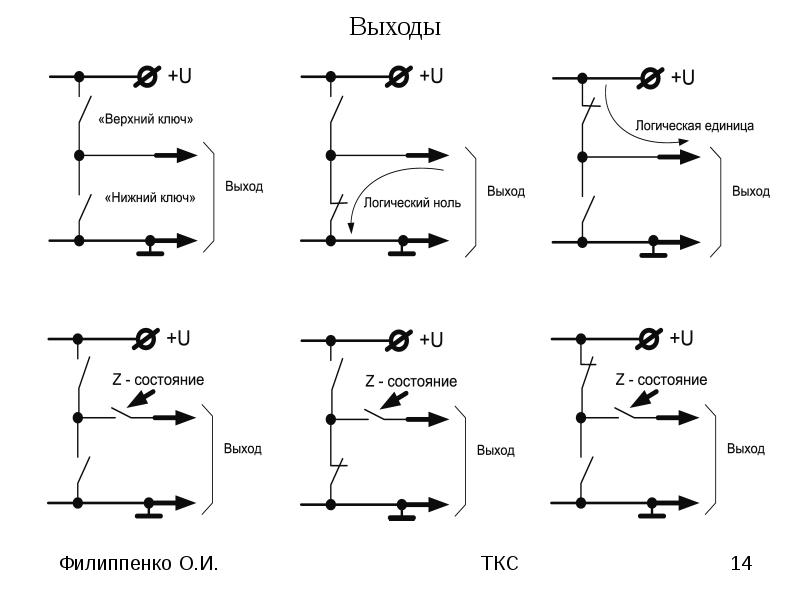

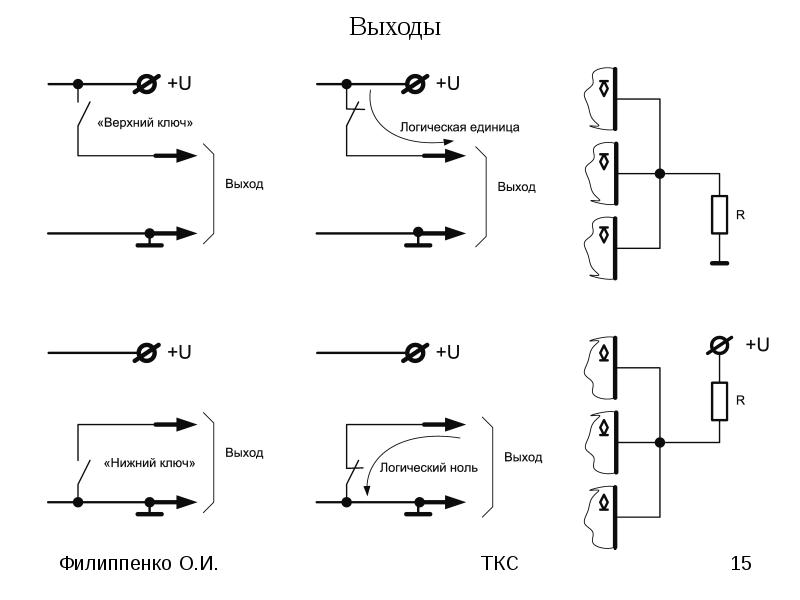

Содержание слайда: Условные обозначения. Выходы.

Прямой статический выход

Инверсный статический выход

Вывод, не несущий логической информации

Открытый вывод (Э, К или И, С)

Открытый выход типа High (присутствует «верхний» ключ)

Открытый выход типа Low (присутствует «нижний» ключ)

Выход с третьим (высокоимпедансным “Z”) состоянием

№24 слайд

Содержание слайда: Задержки

Время нарастания ttLH (transition time low -high) и время спада ttHL (transition High - low) определяются интервалами, границы которых соответствуют 10% и 90% максимальной амплитуды напряжения.

Время задержки распространения при переходе от уровня low к уровню high tpLH (propagation delay time low - high) и время задержки распространения при переходе от уровня high к low tpHL (propagation delay high - low) определяются как интервалы времени между моментом времени соответствующим уровню напряжения на входе, равному 50% максимального напряжения на входе и моментом достижения такого же уровня напряжения на выходе. Время задержки распространения сигнала в логическом вентиле представляет собой среднее значение упомянутых выше интервалов времени.

№25 слайд

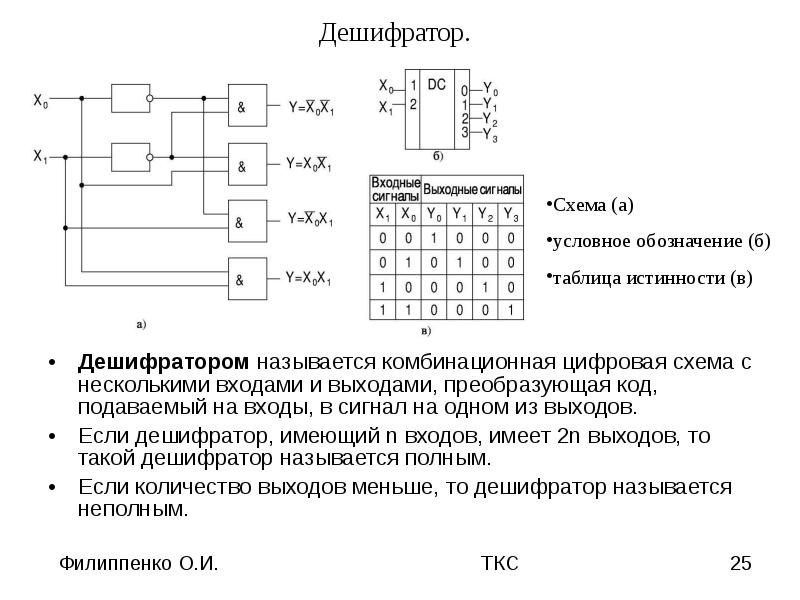

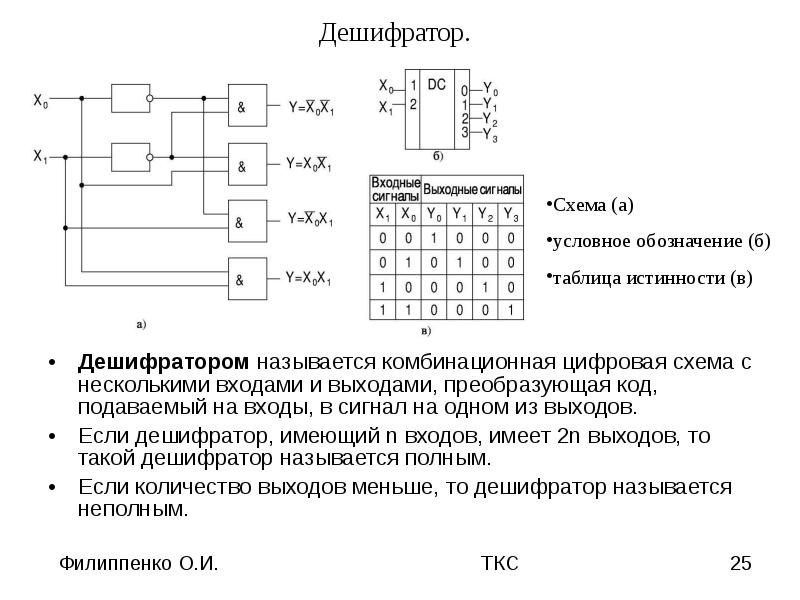

Содержание слайда: Дешифратор.

Дешифратором называется комбинационная цифровая схема с несколькими входами и выходами, преобразующая код, подаваемый на входы, в сигнал на одном из выходов.

Если дешифратор, имеющий n входов, имеет 2n выходов, то такой дешифратор называется полным.

Если количество выходов меньше, то дешифратор называется неполным.

№26 слайд

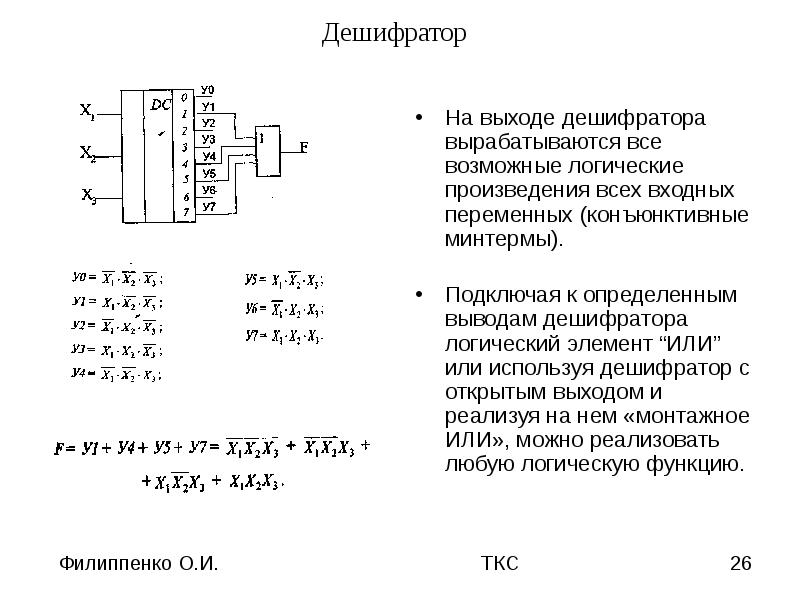

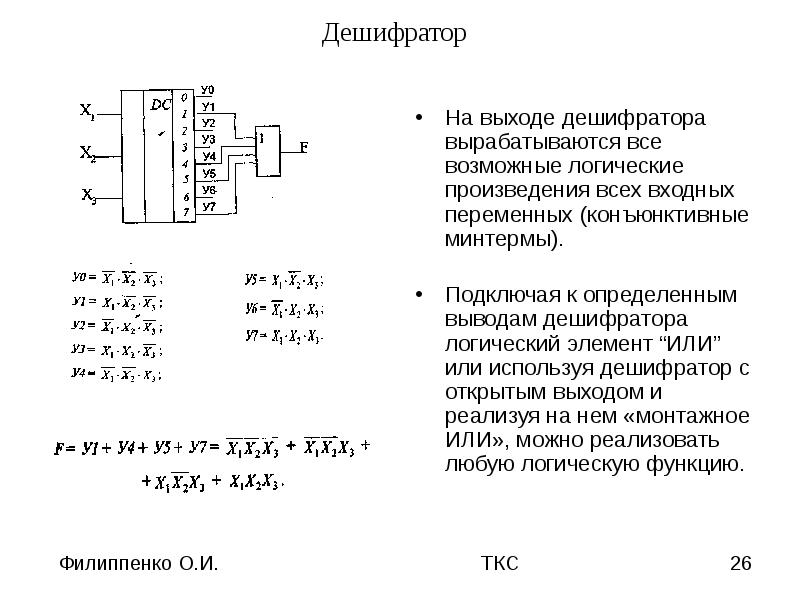

Содержание слайда: Дешифратор

На выходе дешифратора вырабатываются все возможные логические произведения всех входных переменных (конъюнктивные минтермы).

Подключая к определенным выводам дешифратора логический элемент “ИЛИ” или используя дешифратор с открытым выходом и реализуя на нем «монтажное ИЛИ», можно реализовать любую логическую функцию.

№28 слайд

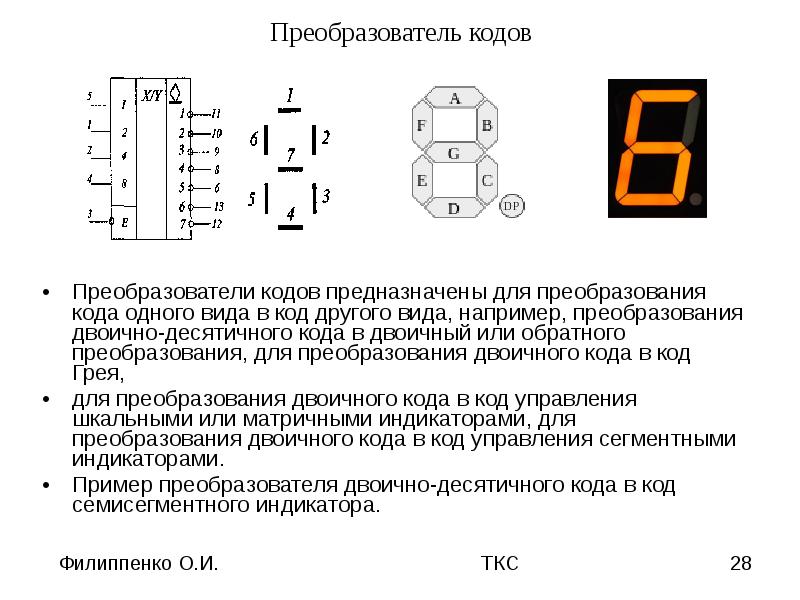

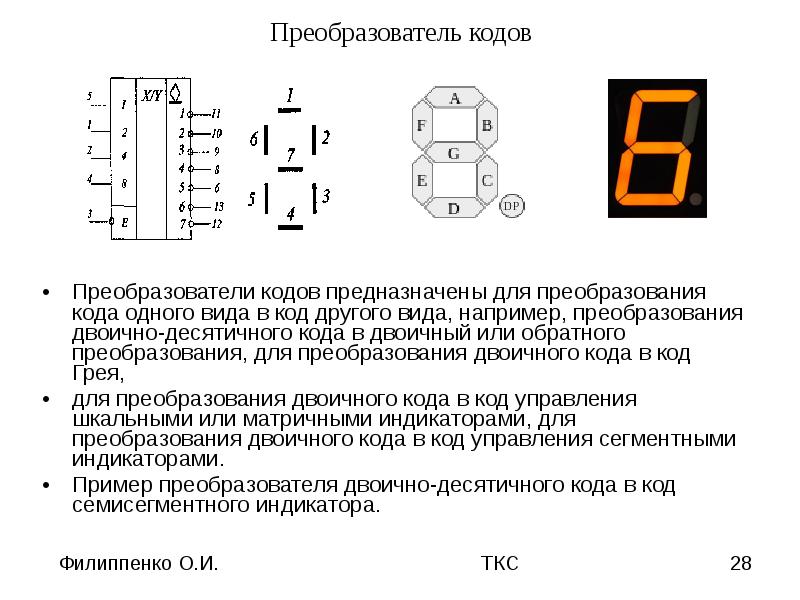

Содержание слайда: Преобразователь кодов

Преобразователи кодов предназначены для преобразования кода одного вида в код другого вида, например, преобразования двоично-десятичного кода в двоичный или обратного преобразования, для преобразования двоичного кода в код Грея,

для преобразования двоичного кода в код управления шкальными или матричными индикаторами, для преобразования двоичного кода в код управления сегментными индикаторами.

Пример преобразователя двоично-десятичного кода в код семисегментного индикатора.

№29 слайд

Содержание слайда: Мультиплексор.

Мультиплексор имеет один выход, информационные входы и адресные или управляющие входы.

В зависимости от кода, подаваемого в адресные шины X0, X1 один из информационных входов подключается к выходному каналу.

Функция алгебры логики, описывающая работу мультиплексора, имеет вид:

№30 слайд

Содержание слайда: Демультиплексор.

Демультиплексором называется комбинационное логическое устройство, предназначенное для управляемой передачи данных от одного источника информации в несколько выходных каналов.

Демультиплексор имеет один информационный вход, n адресных шин и 2n - выходов.

№31 слайд

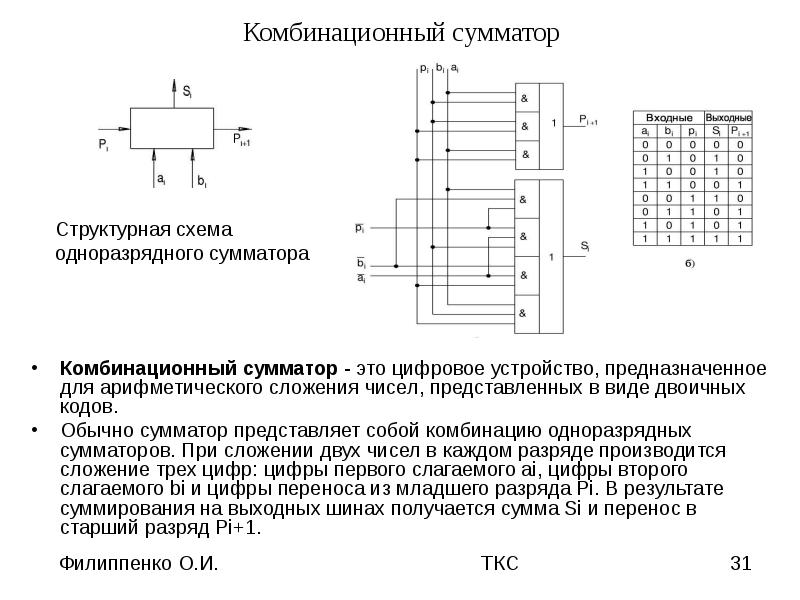

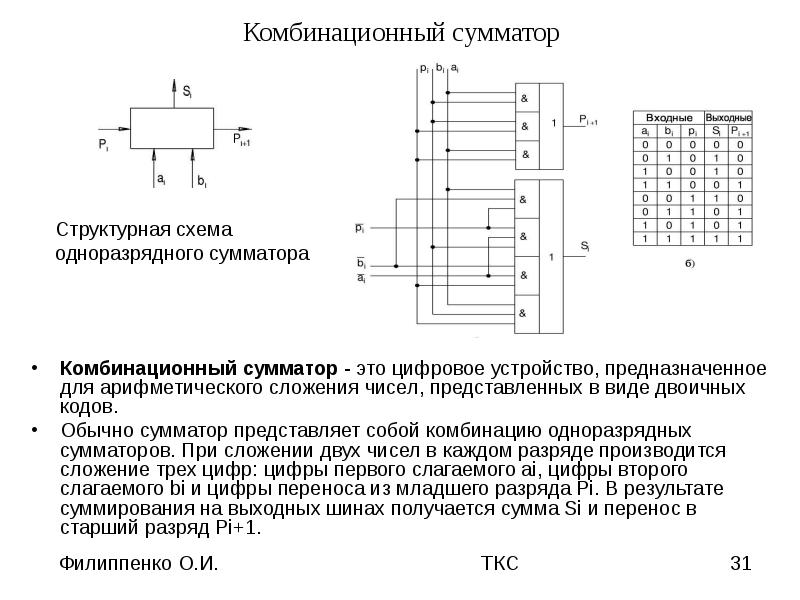

Содержание слайда: Комбинационный сумматор

Комбинационный сумматор - это цифровое устройство, предназначенное для арифметического сложения чисел, представленных в виде двоичных кодов.

Обычно сумматор представляет собой комбинацию одноразрядных сумматоров. При сложении двух чисел в каждом разряде производится сложение трех цифр: цифры первого слагаемого ai, цифры второго слагаемого bi и цифры переноса из младшего разряда Pi. В результате суммирования на выходных шинах получается сумма Si и перенос в старший разряд Pi+1.

№32 слайд

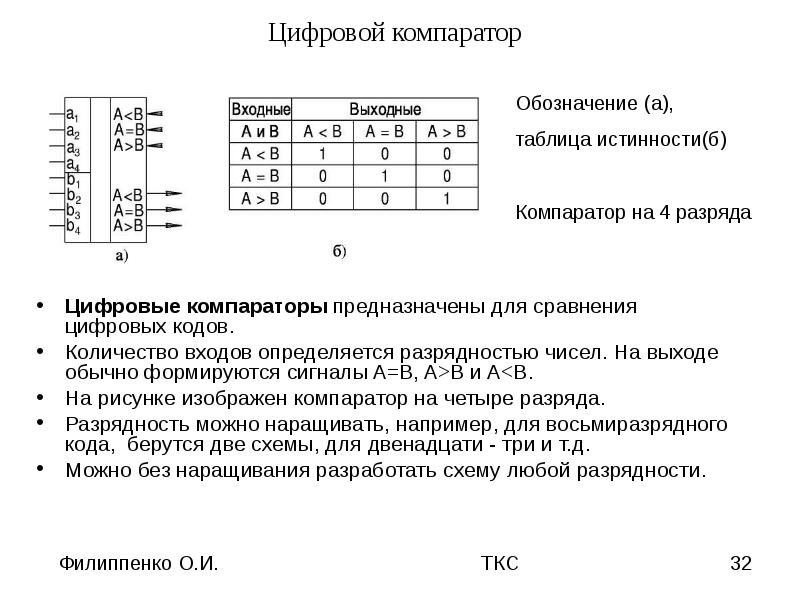

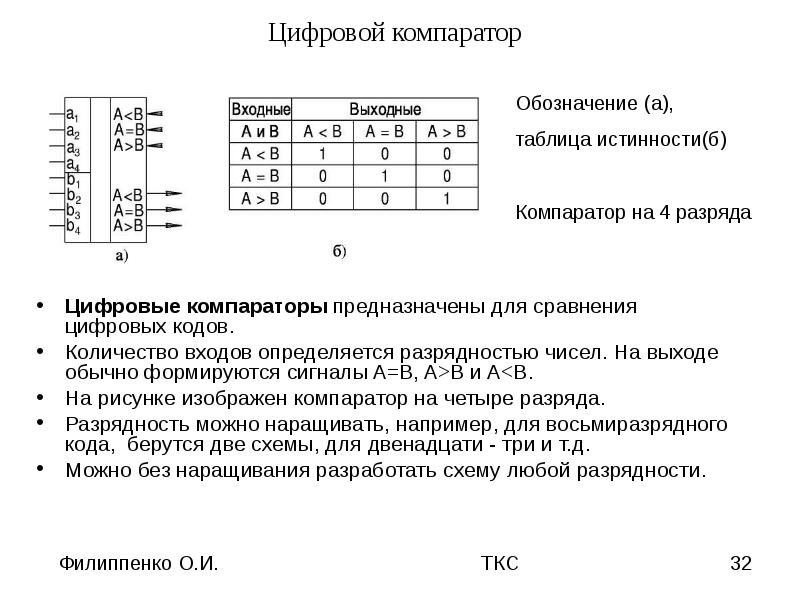

Содержание слайда: Цифровой компаратор

Цифровые компараторы предназначены для сравнения цифровых кодов.

Количество входов определяется разрядностью чисел. На выходе обычно формируются сигналы A=B, A>B и A<B.

На рисунке изображен компаратор на четыре разряда.

Разрядность можно наращивать, например, для восьмиразрядного кода, берутся две схемы, для двенадцати - три и т.д.

Можно без наращивания разработать схему любой разрядности.

№33 слайд

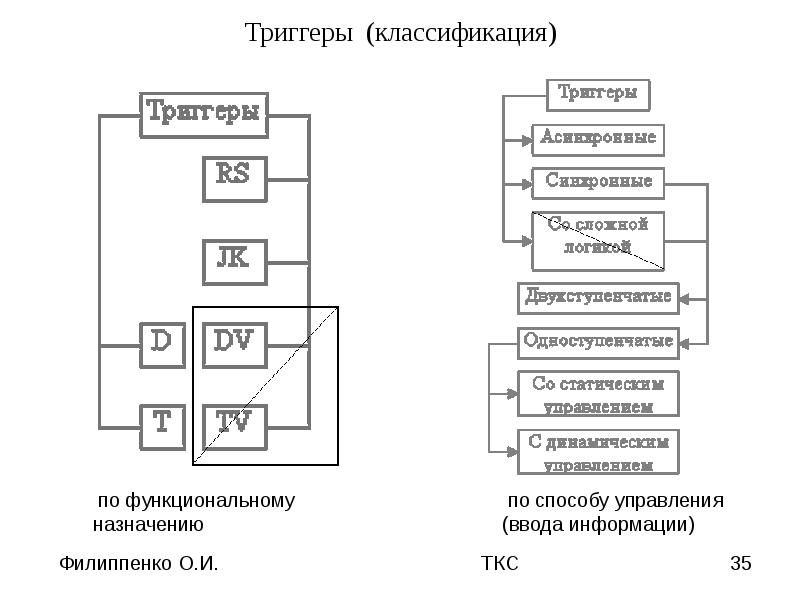

Содержание слайда: Триггеры

Триггером называется цифровое устройство, которое может находиться в одном из двух устойчивых состояний и переходит из одного состояния в другое под действием входных сигналов.

Триггеры можно классифицировать по способу управления (приема информации), принципу построения, функциональным возможностям.

По способу приема информации триггеры подразделяются на асинхронные и синхронные.

Асинхронный триггер изменяет свое состояние в момент прихода сигнала на его информационные входы.

Синхронные триггеры изменяют свое состояние по закону входных сигналов только в момент прихода активного сигнала на его синхронизирующий вход.

Если хотя бы с одного входа информация в триггер заносится под воздействием синхронизирующего сигнала, триггер называется синхронным.

№34 слайд

Содержание слайда: Триггеры

По виду активного сигнала, действующего на информационных входах триггеры подразделяются на статические и динамические.

Статические переключаются потенциалом (уровнем напряжения)

Динамические - перепадом (передним или задним фронтом импульса).

Входные информационные сигналы могут быть прямыми и инверсными.

По принципу построения триггеры можно подразделить на одноступенчатые и двухступенчатые (mastr-slave).

В одноступенчатых триггерах имеется одна ступень запоминания.

В двухступенчатых триггерах имеются две ступени запоминания. Вначале информация записывается в первую ступень, а затем переписывается во вторую и появляется на выходе. В обозначении таких триггеров дублируется символ ТТ

По функциональным возможностям триггеры делятся на: RS-триггер, D-триггер, Т-триггер, JK-триггер, (DV и TV-триггеры).

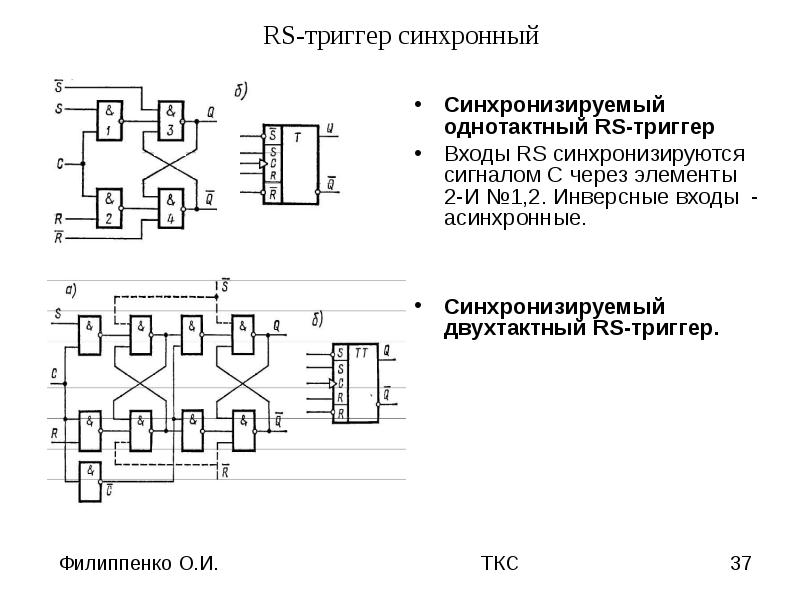

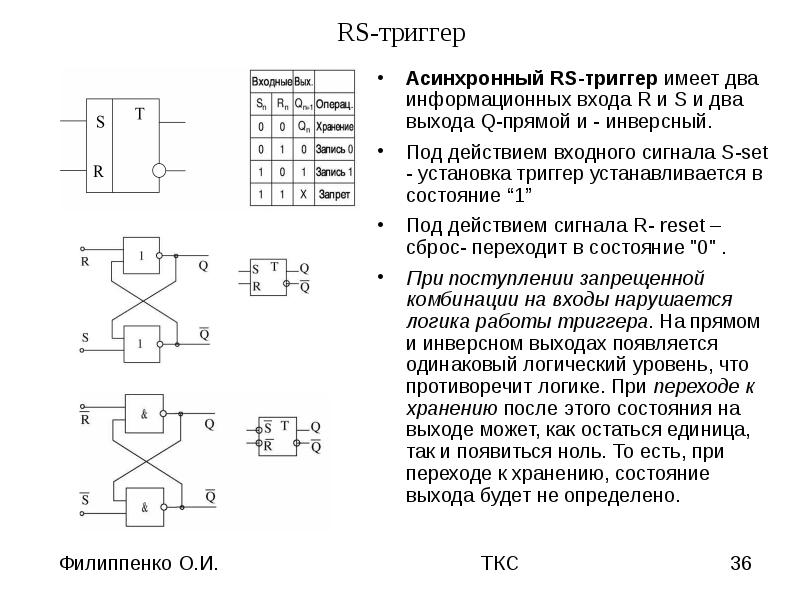

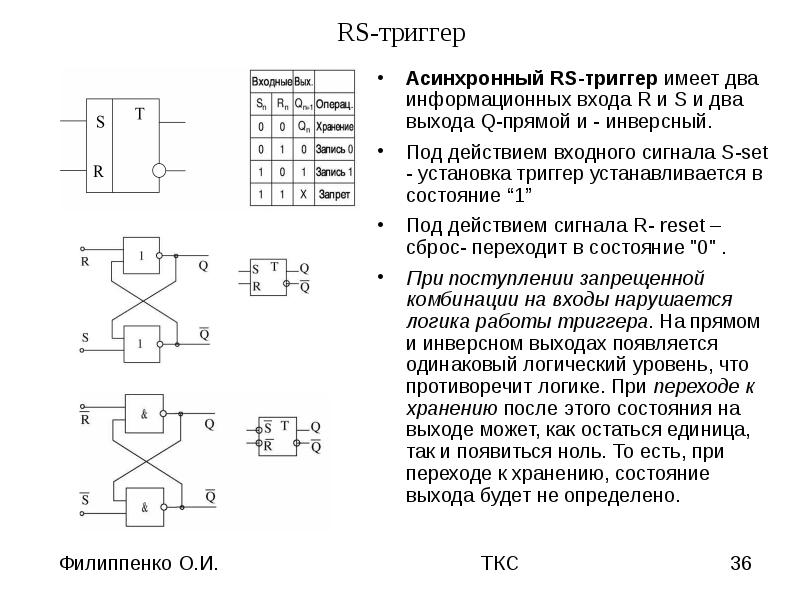

№36 слайд

Содержание слайда: RS-триггер

Асинхронный RS-триггер имеет два информационных входа R и S и два выхода Q-прямой и - инверсный.

Под действием входного сигнала S-set - установка триггер устанавливается в состояние “1”

Под действием сигнала R- reset – сброс- переходит в состояние "0" .

При поступлении запрещенной комбинации на входы нарушается логика работы триггера. На прямом и инверсном выходах появляется одинаковый логический уровень, что противоречит логике. При переходе к хранению после этого состояния на выходе может, как остаться единица, так и появиться ноль. То есть, при переходе к хранению, состояние выхода будет не определено.

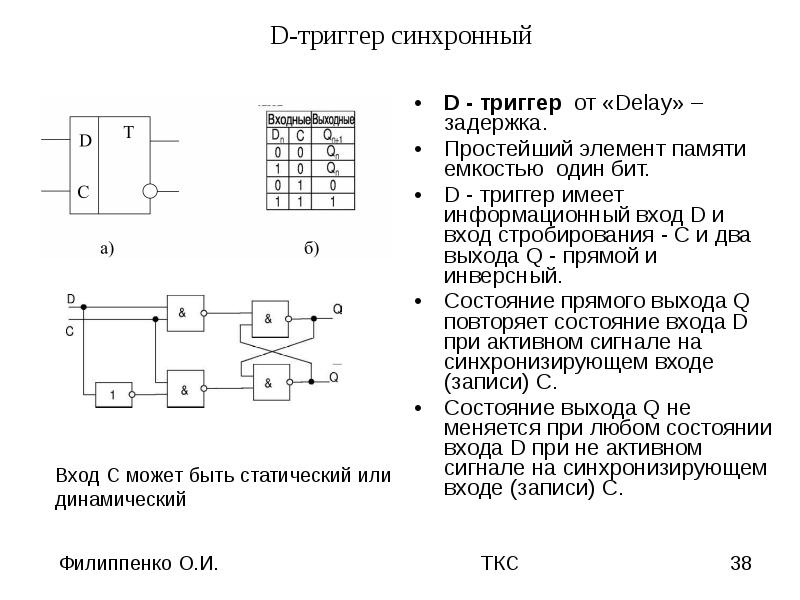

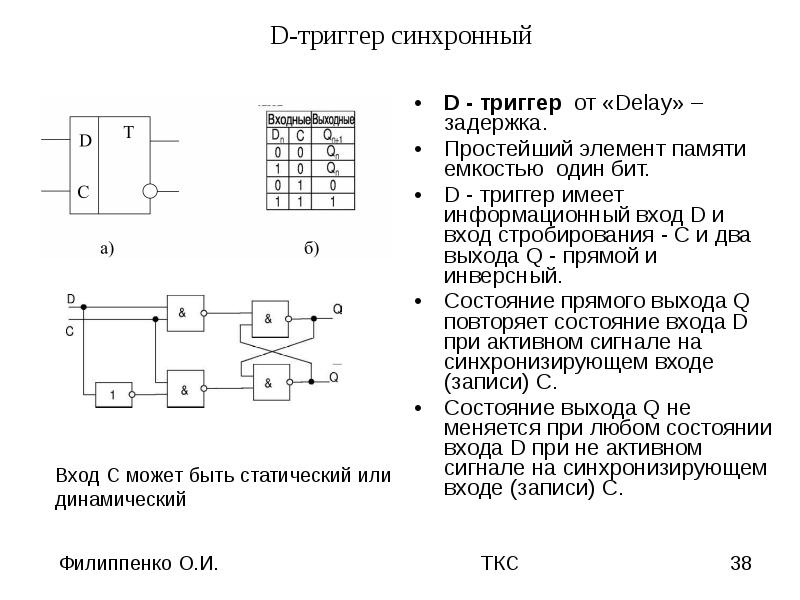

№38 слайд

Содержание слайда: D-триггер синхронный

D - триггер от «Delay» – задержка.

Простейший элемент памяти емкостью один бит.

D - триггер имеет информационный вход D и вход стробирования - С и два выхода Q - прямой и инверсный.

Состояние прямого выхода Q повторяет состояние входа D при активном сигнале на синхронизирующем входе (записи) C.

Состояние выхода Q не меняется при любом состоянии входа D при не активном сигнале на синхронизирующем входе (записи) C.

№39 слайд

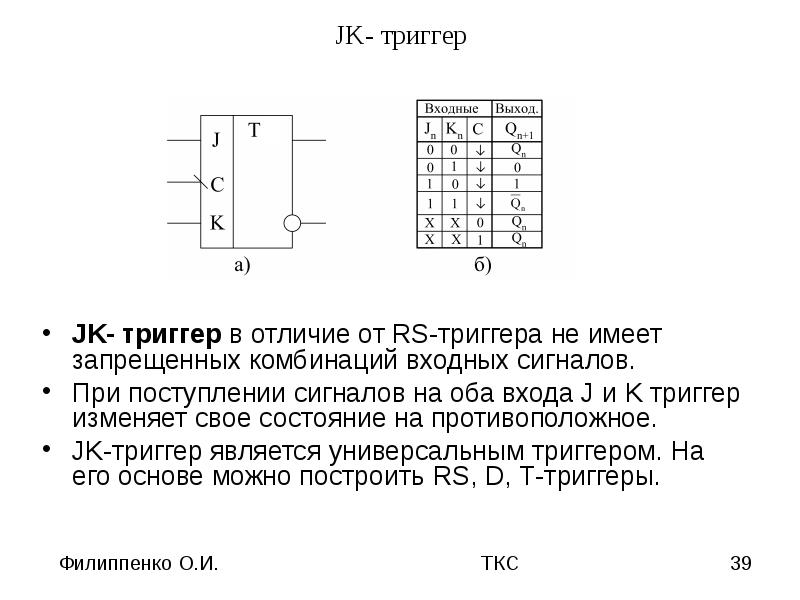

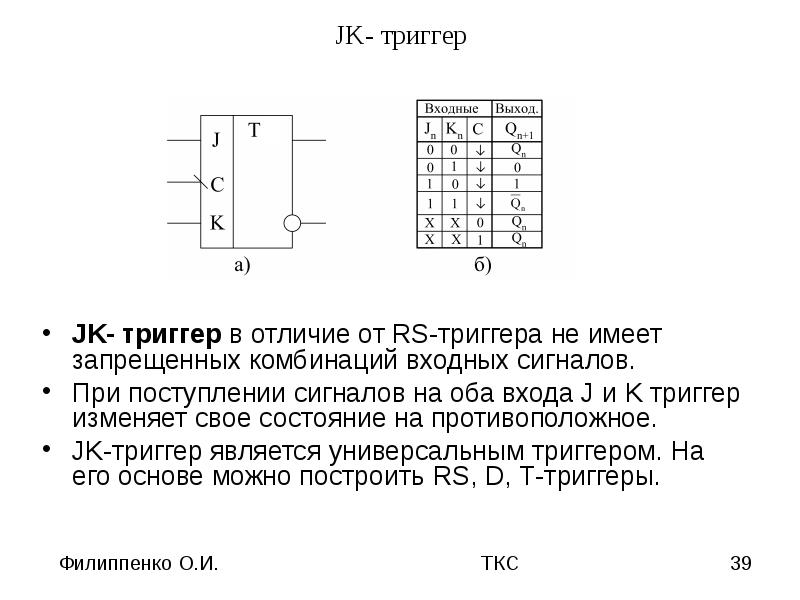

Содержание слайда: JK- триггер

JK- триггер в отличие от RS-триггера не имеет запрещенных комбинаций входных сигналов.

При поступлении сигналов на оба входа J и K триггер изменяет свое состояние на противоположное.

JK-триггер является универсальным триггером. На его основе можно построить RS, D, Т-триггеры.

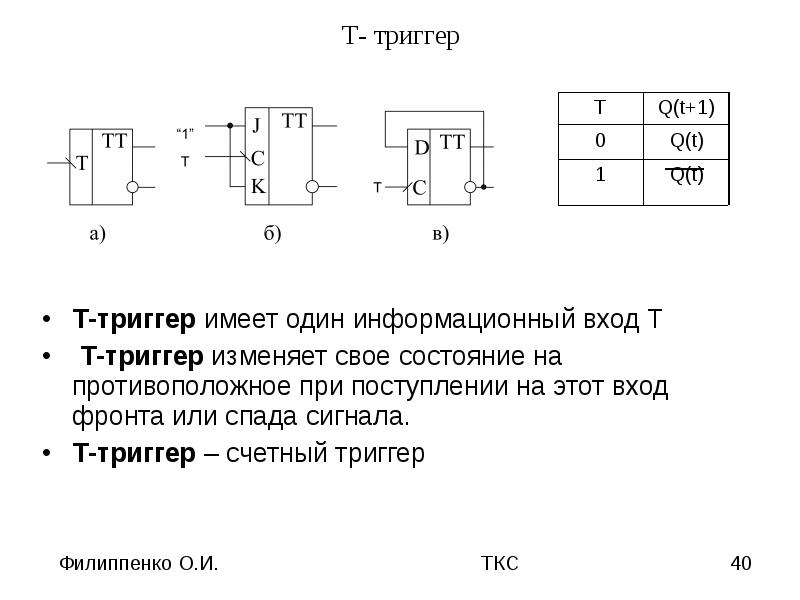

№41 слайд

Содержание слайда: Регистр

Регистр — функциональное устройство, предназначенное для приема (записи) и запоминания n-разрядного слова (кода), а также для выполнения определенных микроопераций, например – сдвиг, над этим словом.

Регистр представляет собой упорядоченную совокупность триггеров со схемой управления входными и выходными сигналами.

С помощью регистров можно осуществлять операции преобразования информации из одного вида в другой (последовательного кода в параллельный и т. п.).

При помощи объединения схемы управления (комбинационной схемы) и регистра можно осуществить различные операции, например:

ввод и вывод из регистра хранимой информации;

преобразование кода числа, хранящегося в регистре;

сдвиг числа влево или вправо на определенное число разрядов;

преобразование последовательного кода числа в параллельный и наоборот

и т.д.

№42 слайд

Содержание слайда: Регистры

Регистры классифицируют по различным признакам, основными из которых являются:

способ ввода информации (записи) в регистр и ее вывод,

способ представления вводимой и выводимой информации.

По способу ввода и вывода информации регистры подразделяются на:

параллельные (регистры памяти);

последовательные (регистры сдвига);

параллельно-последовательные.

№43 слайд

Содержание слайда: Параллельный регистр

В параллельных регистрах запись информации производится в параллельном коде одновременно по всем разрядам.

Параллельные регистры применяются, например, для хранения информации и поэтому называются еще регистрами памяти.

Параллельный регистр может быть выполнен, например, на D-триггерах.

Если вход записи динамический, запись информации производится по фронту тактового сигнала.

Если вход записи статический, то при активном уровне на нем, происходит прямая передача информации с входов на выходы, а при смене сигнала на не активный уровень – фиксация данных, которые присутствовали на входе в момент смены уровня сигнала записи.

На входах и выходах триггеров регистра могут стоять логические схемы для преобразования кодов в прямые или инверсные.

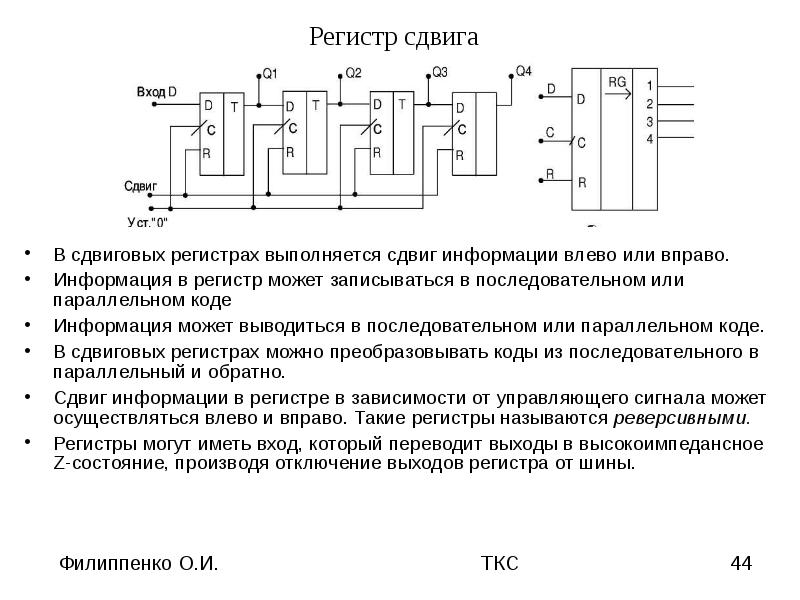

№44 слайд

Содержание слайда: Регистр сдвига

В сдвиговых регистрах выполняется сдвиг информации влево или вправо.

Информация в регистр может записываться в последовательном или параллельном коде

Информация может выводиться в последовательном или параллельном коде.

В сдвиговых регистрах можно преобразовывать коды из последовательного в параллельный и обратно.

Сдвиг информации в регистре в зависимости от управляющего сигнала может осуществляться влево и вправо. Такие регистры называются реверсивными.

Регистры могут иметь вход, который переводит выходы в высокоимпедансное Z-состояние, производя отключение выходов регистра от шины.

№45 слайд

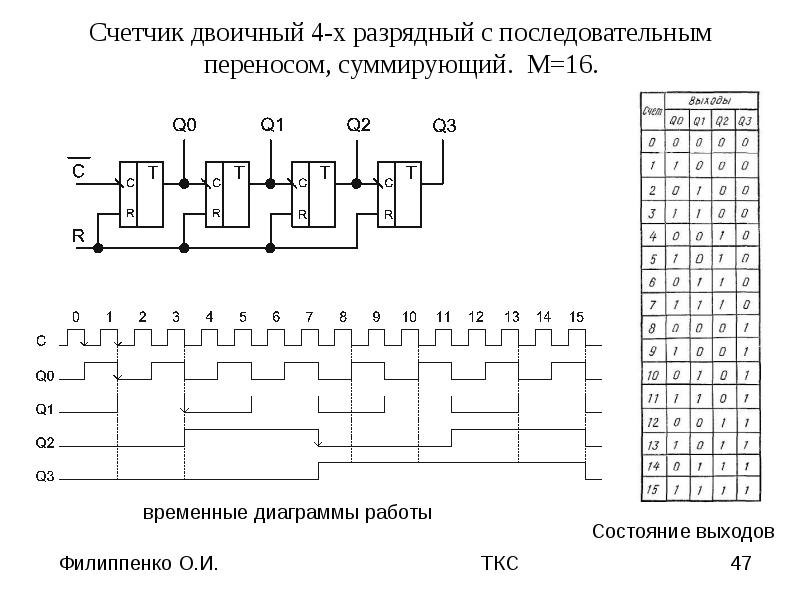

Содержание слайда: Счетчики

Счетчик представляет собой устройство, предназначенное для подсчета числа сигналов, поступающих на его вход, и фиксации этого числа в виде кода, хранящегося в триггерах.

Количество разрядов счетчика определяется наибольшим числом, которое должно быть получено в результате счета.

Для счета и выдачи результатов в счетчиках имеется один вход и n выходов в зависимости от количества разрядов.

В общем случае счетчик имеет М=2n устойчивых состояний, включая нулевое.

Счетчик, установленный в определенное состояние, сохраняет его до тех пор, пока на вход не поступит следующий сигнал.

Каждому состоянию счетчика соответствует порядковый номер 0, 1, 2,..., М—1.

При подаче на вход счетчика М-го входного сигнала на выходе его возникает сигнал переполнения и счетчик возвращается в начальное состояние, т. е. счет единичных сигналов осуществляется в нем по модулю М.

Модуль М называется коэффициентом пересчета.

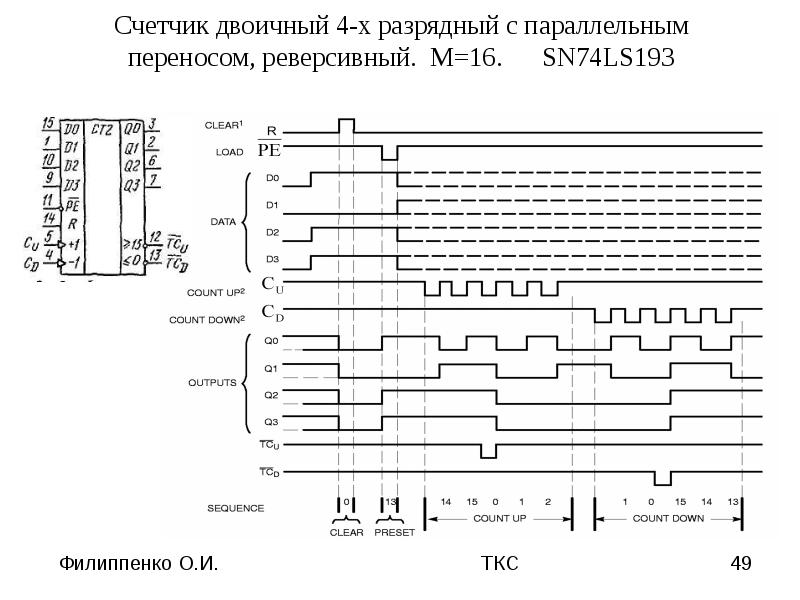

№46 слайд

Содержание слайда: Счетчики

Счетчики бывают суммирующие, вычитающие и реверсивные.

Суммирующий счетчик предназначен для выполнения счета в прямом направлении, т. е. для суммирования входных импульсов.

Вычитающий счетчик предназначен для выполнения счета в сторону уменьшения, т.е. в режиме вычитания.

Реверсивный счетчик имеет вход управления, позволяющий изменять направление счета.

По способу организации межразрядных связей счетчики выполняются с:

последовательным переносом,

параллельным переносом и

параллельно-последовательным переносом.

Самые простые и вместе с тем самые медленные - это счетчики с последовательным переносом.

Наибольшим быстродействием обладают счетчики с параллельным переносом.

№48 слайд

Содержание слайда: Счетчики с произвольным коэффициентом пересчета

Счетчики с произвольным коэффициентом пересчета можно построить на основе двоичных счетчиков с организацией обратной связи с выходов соответствующих разрядов через схему И (дешифратор) на вход R- обнуления счетчика.

Счетчики с произвольным коэффициентом пересчета можно построить на вычитающих счетчиках в режиме автоматической перезагрузки по сигналу заема.

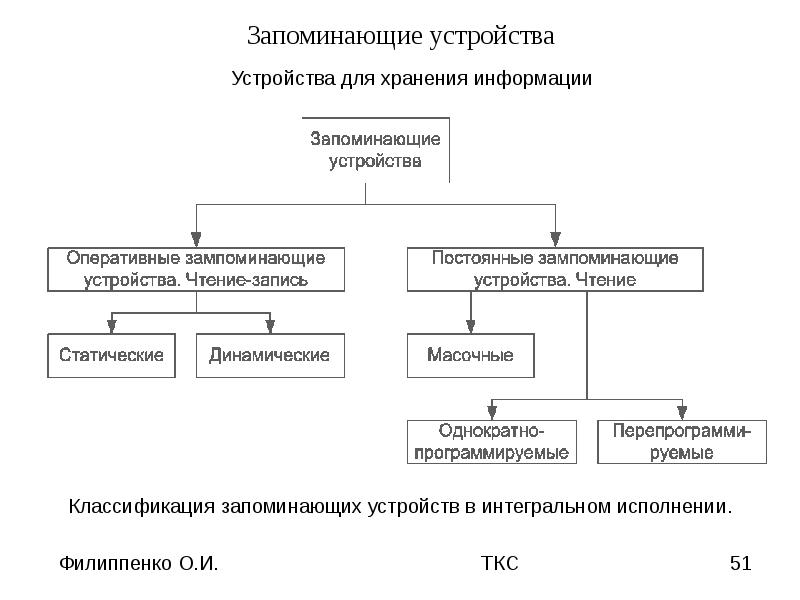

№52 слайд

Содержание слайда: Постоянное запоминающее устройство (ПЗУ)

Постоянное запоминающее устройство (ПЗУ) - энергонезависимое ЗУ, которое служит для хранения стандартных (неизменяемых) программ и констант, необходимых для выполнения программы.

В ПЗУ обычно записываются программы начальной инициализации (загрузки) систем, тестовые и диагностические программы и другое служебное программное обеспечение, которое не меняется в процессе эксплуатации систем.

В микропроцессорных системах, управляющих определенными объектами с использованием фиксированных или редко изменяемых программ, для их хранения также обычно используется ПЗУ (память ROM - Read-Only Memory) или репрограммируемое ПЗУ (память EEPROM - Electrically Erased Programmable Read-Only Memory или флэш-память).

Масочные ПЗУ программируются исключительно в условиях полупроводникового производства.

Механизмов занесения информации в программируемые ПЗУ существует несколько.

№53 слайд

Содержание слайда: Основные принципы хранения информации

Физически пережигаемые перемычки матрицы на основе нихрома или поликристаллического кремния (ограниченное применение)

Элементы памяти на полевых транзисторах с плавающими (не имеющими выводов, находящиеся в толще диэлектрика между управляющим затвором и каналом) затворами с лавинно-инжекционным накоплением зарядов.

Различают приборы, в которых элементарная ячейка хранит один бит информации и несколько бит.

В однобитовых ячейках различают только два уровня заряда на плавающем затворе. Такие ячейки называют одноуровневыми (single-level cell, SLC).

В многобитовых ячейках различают больше уровней заряда; их называют многоуровневыми (multi-level cell, MLC). MLC-приборы дешевле и более ёмкие, чем SLC-приборы, однако с большим временем доступа и меньшим максимальным количеством перезаписей.

MLC память может быть с 4 уровнями заряда (2 бита) на каждую ячейку, память с 8 уровнями (3 бита) иногда называют TLC (Triple Level Cell) или 3bit MLC и более.

№54 слайд

Содержание слайда: Оперативное запоминающее устройство (ОЗУ)

Оперативное запоминающее устройство (ОЗУ) - энергозависимое ЗУ, которое служит для хранения данных, получаемых в результате выполнения программы.

В оперативное запоминающее устройство (для принстонской архитектуры) также возможна загрузка программы или части программы и передача управления этому фрагменту программы, т.е. в ОЗУ может хранится выполняемая программа (или ее фрагменты), а также данные, подлежащих обработке. Информация, находящаяся в ОЗУ теряется при снятии питающего напряжения.

Элементами памяти в статических ЗУ, как правило, являются триггеры. Один триггер может запомнить один бит информации. После записи информации в ячейку для обеспечения хранения не требуется никаких дополнительных действий до следующей записи. Чтение не влияет на состояние ячеек памяти. Память такого типа имеет высокую стоимость в силу большого количества транзисторов необходимых для построения одной ячейки памяти. При снятии питания информация разрушается.

№55 слайд

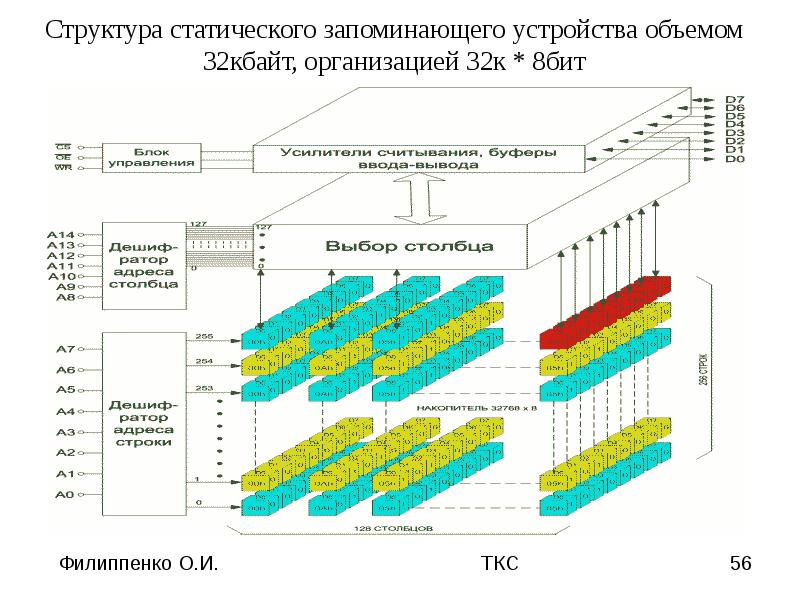

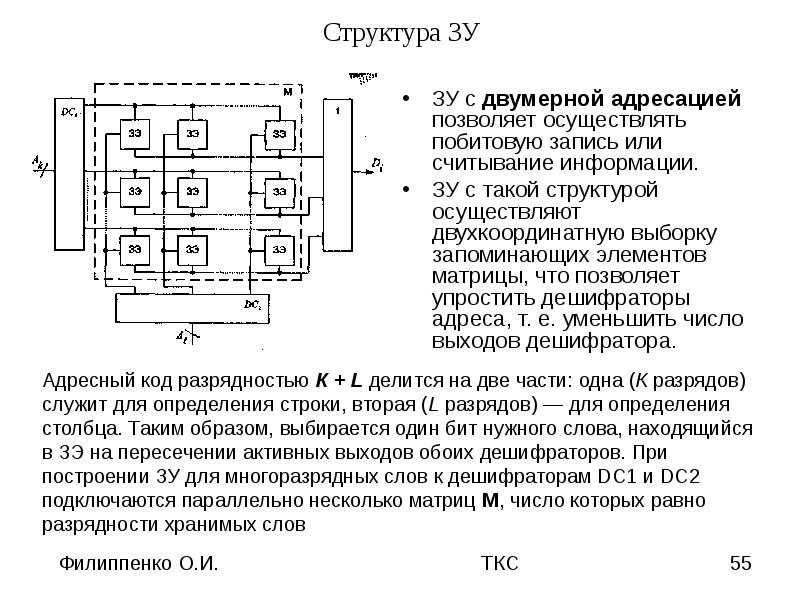

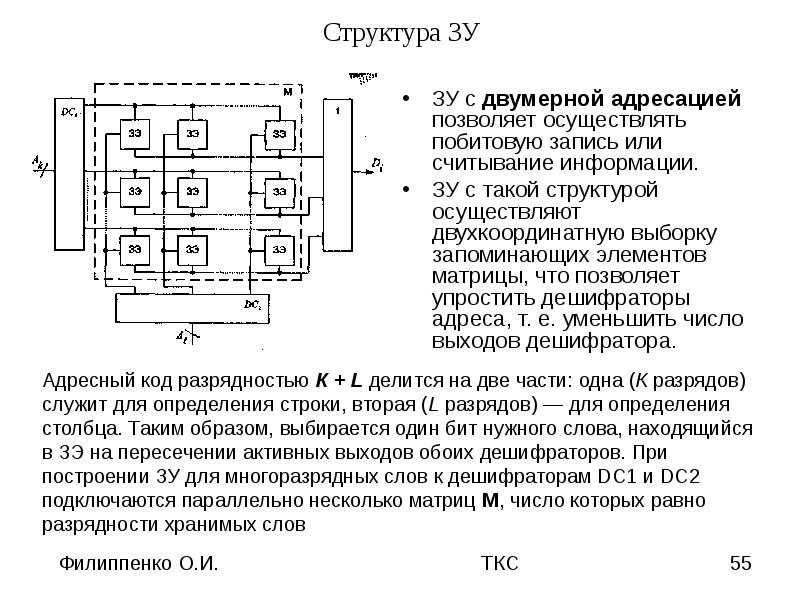

Содержание слайда: Структура ЗУ

ЗУ с двумерной адресацией позволяет осуществлять побитовую запись или считывание информации.

ЗУ с такой структурой осуществляют двухкоординатную выборку запоминающих элементов матрицы, что позволяет упростить дешифраторы адреса, т. е. уменьшить число выходов дешифратора.

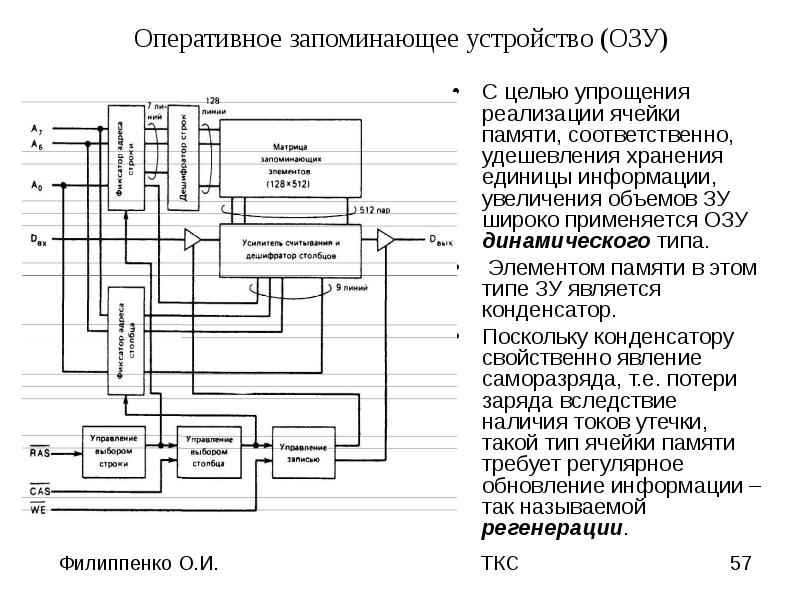

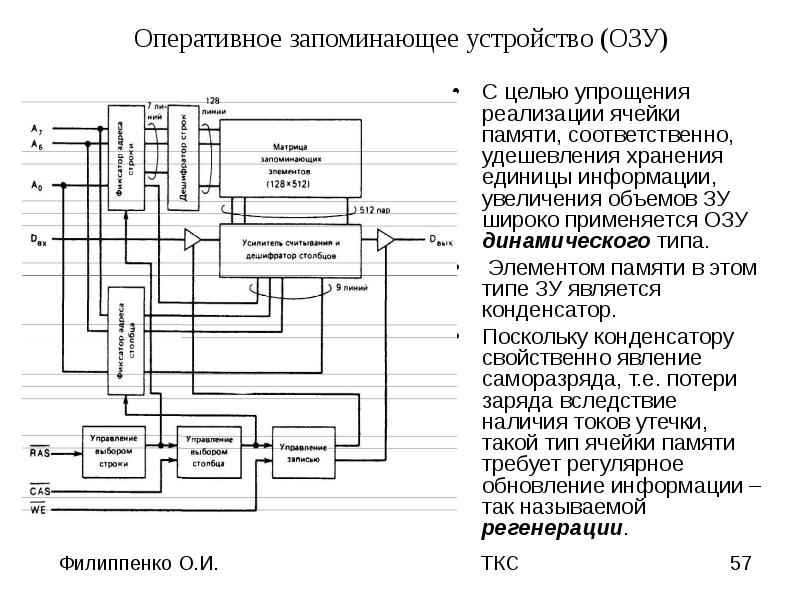

№57 слайд

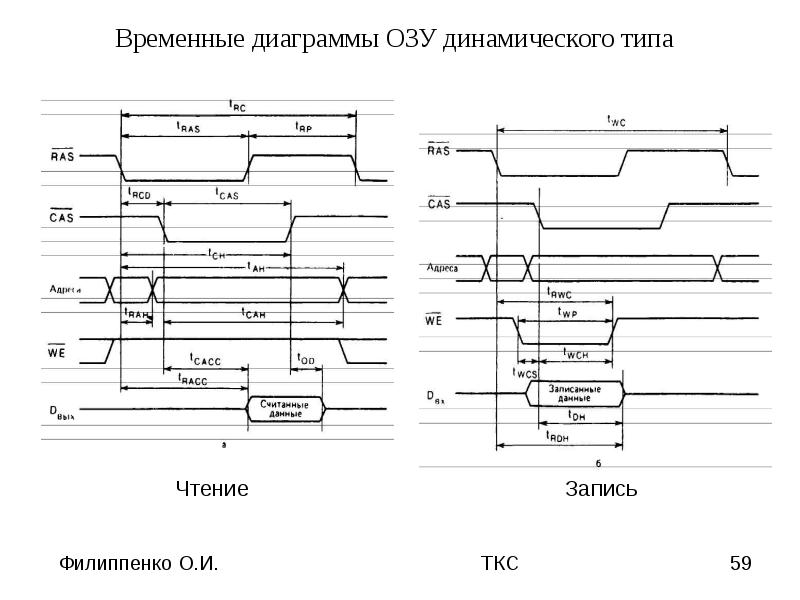

Содержание слайда: Оперативное запоминающее устройство (ОЗУ)

С целью упрощения реализации ячейки памяти, соответственно, удешевления хранения единицы информации, увеличения объемов ЗУ широко применяется ОЗУ динамического типа.

Элементом памяти в этом типе ЗУ является конденсатор.

Поскольку конденсатору свойственно явление саморазряда, т.е. потери заряда вследствие наличия токов утечки, такой тип ячейки памяти требует регулярное обновление информации – так называемой регенерации.

№60 слайд

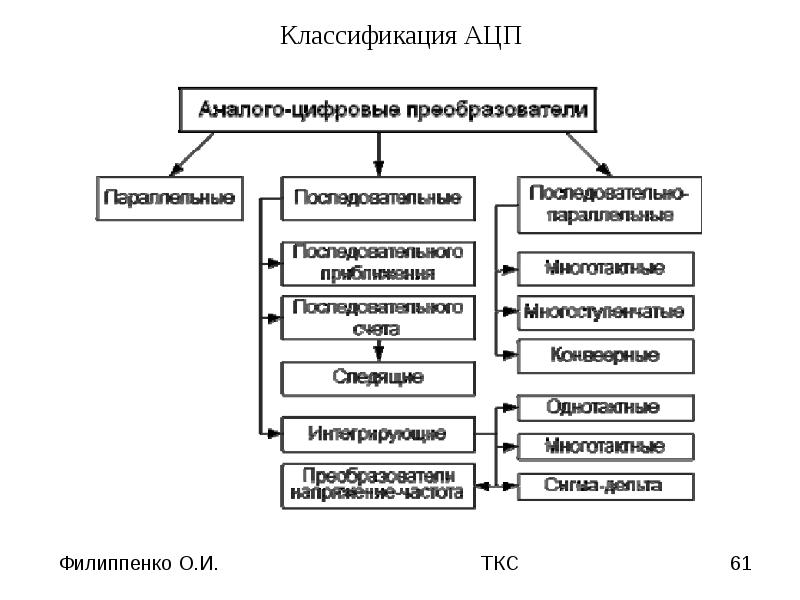

Содержание слайда: АЦП

Аналого-цифровые преобразователи (АЦП) являются устройствами, которые принимают входные аналоговые сигналы и генерируют соответствующие им цифровые сигналы, пригодные для обработки микропроцессорами и другими цифровыми устройствами.

Процедура аналого-цифрового преобразования непрерывных сигналов, которую реализуют с помощью АЦП, представляет собой преобразование непрерывной функции времени U(t), описывающей исходный сигнал, в последовательность чисел {U'(tj)}, j=0,1,2,:, отнесенных к некоторым фиксированным моментам времени.

Эту процедуру можно разделить на две самостоятельные операции.

Первая из них называется дискретизацией и состоит в преобразовании непрерывной функции времени U(t) в непрерывную последовательность {U(tj)}.

Вторая называется квантованием и состоит в преобразовании непрерывной последовательности в дискретную {U'(tj)}.

№62 слайд

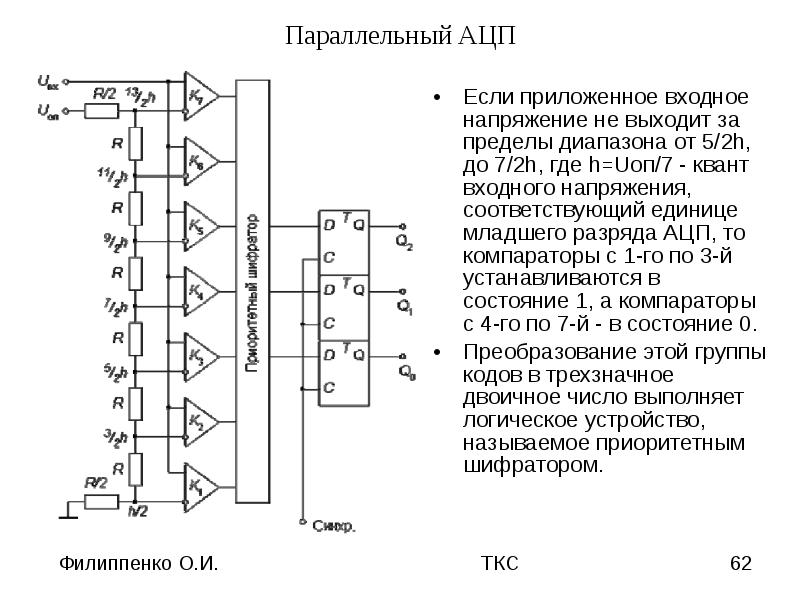

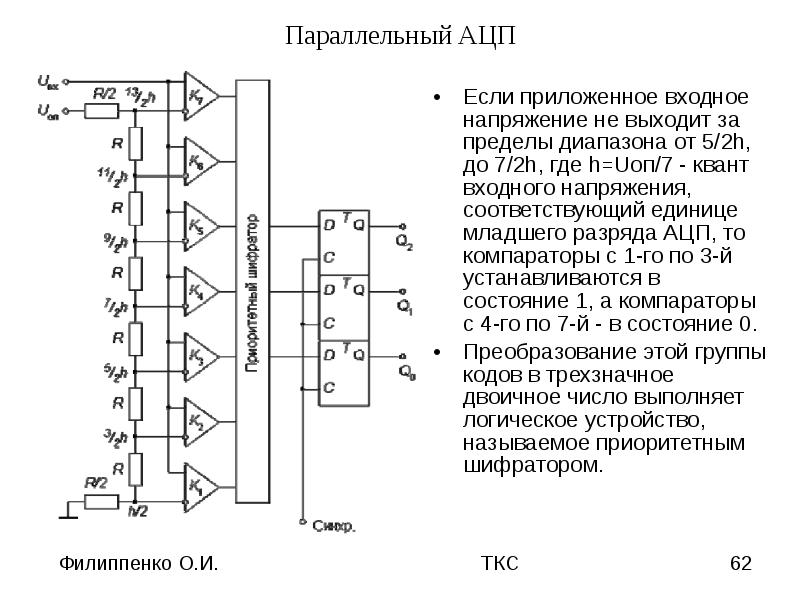

Содержание слайда: Параллельный АЦП

Если приложенное входное напряжение не выходит за пределы диапазона от 5/2h, до 7/2h, где h=Uоп/7 - квант входного напряжения, соответствующий единице младшего разряда АЦП, то компараторы с 1-го по 3-й устанавливаются в состояние 1, а компараторы с 4-го по 7-й - в состояние 0.

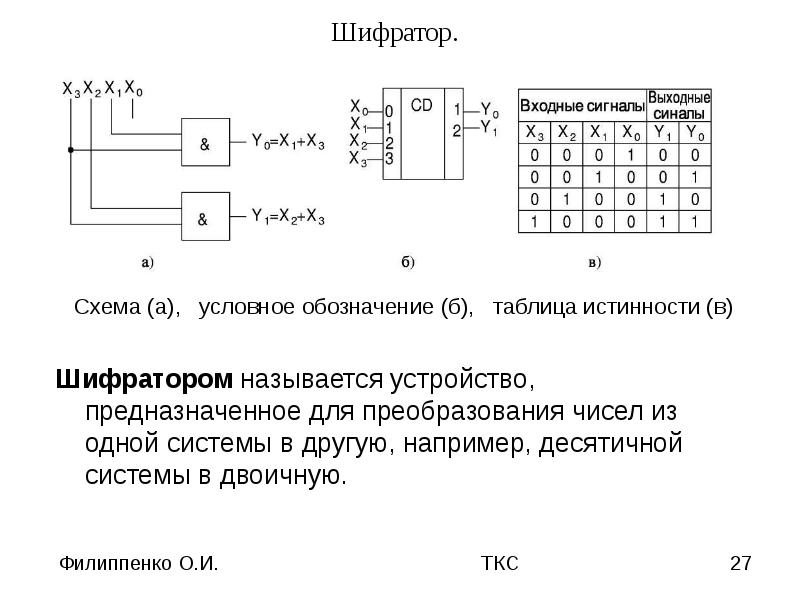

Преобразование этой группы кодов в трехзначное двоичное число выполняет логическое устройство, называемое приоритетным шифратором.

№63 слайд

Содержание слайда: ЦАП

Цифро-аналоговый преобразователь (ЦАП) предназначен для преобразования числа, определенного, как правило, в виде двоичного кода, в напряжение или ток, пропорциональные значению цифрового кода.

Цифро-аналоговые преобразователи можно классифицировать по следующим признакам:

разрядность

по виду выходного сигнала: с токовым выходом и выходом в виде напряжения

по типу цифрового интерфейса: с последовательным вводом и с параллельным вводом входного кода

по быстродействию

Скачать все slide презентации ОТМП. Элементы и узлы ЭВМ. (Тема 2) одним архивом:

Похожие презентации

-

Элементы и узлы ЭВМ. Тригерры

Элементы и узлы ЭВМ. Тригерры -

Микропроцессоры. Логические основы ЭВМ, элементы и узлы

Микропроцессоры. Логические основы ЭВМ, элементы и узлы -

Элементы автомобильных дорог и их влияние на безопасность дорожного движения. Тема 2

Элементы автомобильных дорог и их влияние на безопасность дорожного движения. Тема 2 -

Основные элементы системы газоснабжения населенных пунктов. Система газоснабжения здания. Газовые приборы

Основные элементы системы газоснабжения населенных пунктов. Система газоснабжения здания. Газовые приборы -

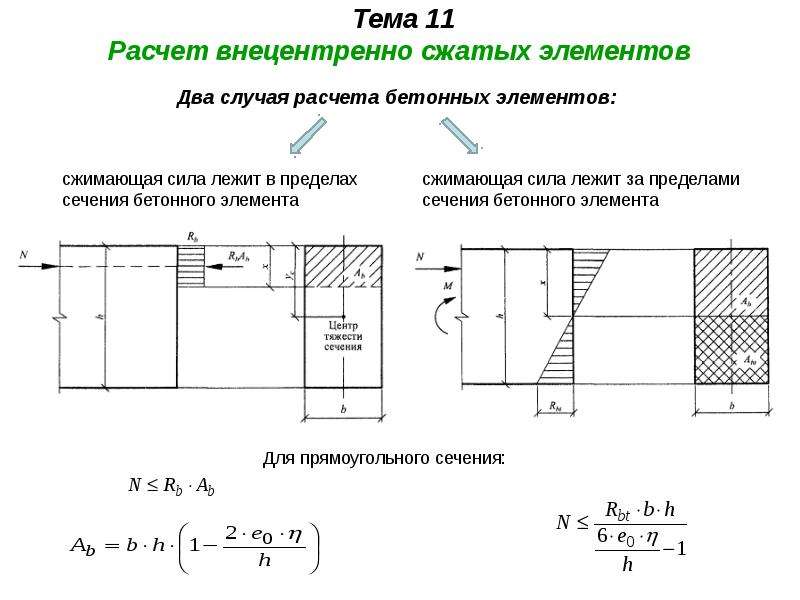

Расчет внецентренно сжатых элементов ЖБК. (Тема 11)

Расчет внецентренно сжатых элементов ЖБК. (Тема 11) -

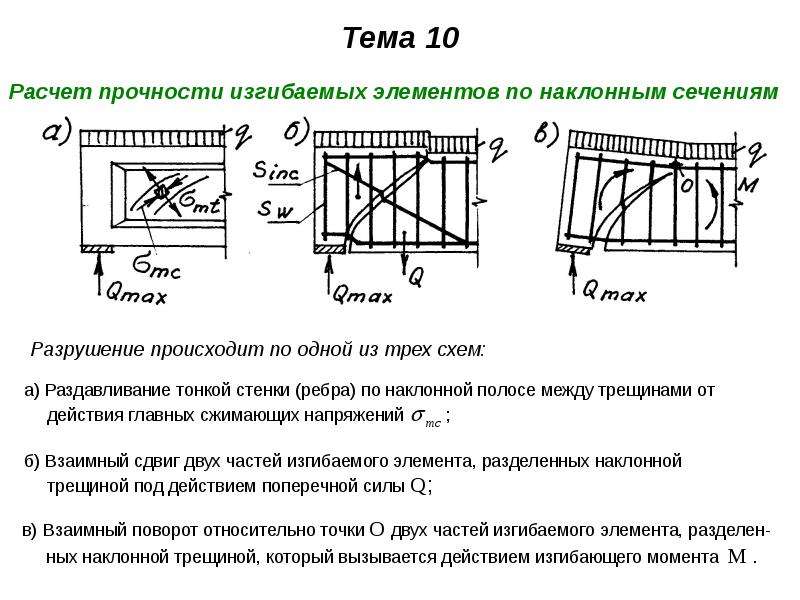

Расчет прочности изгибаемых элементов по наклонным сечениям. (Тема 10)

Расчет прочности изгибаемых элементов по наклонным сечениям. (Тема 10) -

Расчет элементов прямоугольного сечения с одиночной арматурой. (Тема 9)

Расчет элементов прямоугольного сечения с одиночной арматурой. (Тема 9) -

Поколения ЭВМ. Элементная база

Поколения ЭВМ. Элементная база -

Математическое моделирование ППП и элементов ИМС с использованием компактных моделей (часть 1)

Математическое моделирование ППП и элементов ИМС с использованием компактных моделей (часть 1) -

Математическое моделирование электро-физических параметров и элементов ИМС. (Часть 1)

Математическое моделирование электро-физических параметров и элементов ИМС. (Часть 1)