Содержание слайда: FPGA

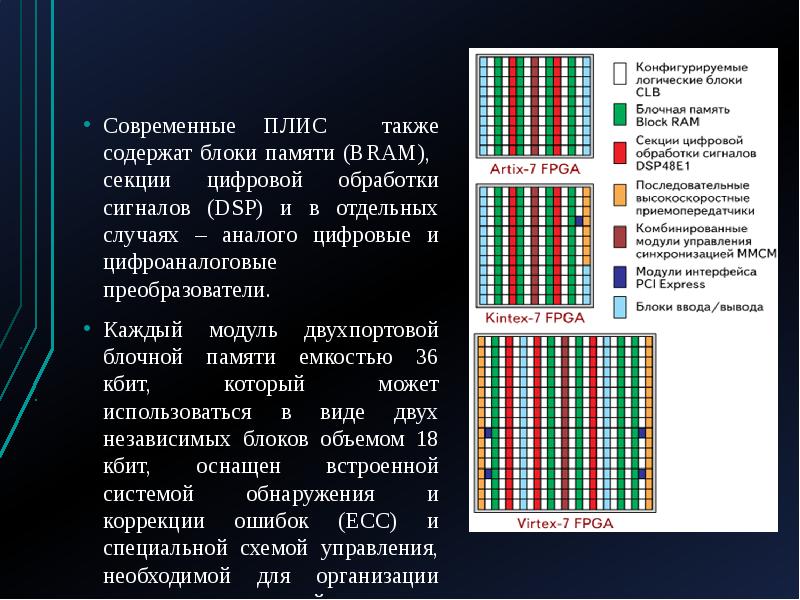

Функциональное назначение FPGA сходно с CPLD, но более высокая гибкость внутренней архитектуры, а также гораздо более высокая логическая вместимость даёт FPGA преимущества во многих областях применения. В основе FPGA лежат логические блоки (или вентили - gates), похожие на переключатели со множеством входов и одним выходом. Эти блоки реализуют базовые двоичные операции: AND, NAND, OR, NOR и XOR. Принципиальным отличием FPGA является то, что и функции самих блоков, и конфигурация их связей между собой могут меняться специальными управляющими схемами. Каждый логический блок имеет несколько входов (4-6) и один выход и основан на таблице поиска (Look Up Table - LUT) - память, используемая для хранения значений простых логических функций. Значения входов LUT задаёт конечную логическую функцию, определяемую выходом. Таким образом применяется подход замены процесса вычисления на операции простого поиска значений.

Так же каждый вентиль имеет синхронизирующий вход, подключённый к отдельным трассировочным путям. Помимо логических блоков каждая FPGA содержит программируемые ключи для создания соединения между вентилями (Interconnection Switches) и блоки ввода-вывода для подключения внутренней схемы к внешним выводам ИС. Между любым соседним вентилем расположен один блок-ключ

FPGA можно использовать лишь тогда, когда логические блоки запрограммированы для реализации необходимых функций, а линии соединений запрограммированы на реализацию требуемых взаимосвязей между логическими блоками и блоками ввода-вывода. Запоминающие ячейки LUT в FPGA энергозависимы. Это означает, что они теряют свое содержимое всякий раз при отключении питания. Следовательно, чип FPGA должен за программироваться каждый раз при включении питания. Обычно, данные, необходимые для программирования хранятся в микросхеме ППЗУ, расположенной на той же плате, что и чип FPGA. Такой "недостаток» может сыграть роль в конкретной разработке, так как это свойство FPGA позволяет создавать адаптивные системы с динамически изменяющейся во времени структурой. То есть, в разные моменты времени использовать один и тот же кристалл для реализации различных цифровых устройств, которые наилучшим образом соответствуют изменяющимся во времени внешним условиям (например, обеспечивать работу сотового телефона в сетях с различными стандартами в зависимости от доступности той или иной сети в данный момент времени).