Презентация Запамятовуючі пристрої СО (Заняття 7. 3) онлайн

На нашем сайте вы можете скачать и просмотреть онлайн доклад-презентацию на тему Запамятовуючі пристрої СО (Заняття 7. 3) абсолютно бесплатно. Урок-презентация на эту тему содержит всего 30 слайдов. Все материалы созданы в программе PowerPoint и имеют формат ppt или же pptx. Материалы и темы для презентаций взяты из открытых источников и загружены их авторами, за качество и достоверность информации в них администрация сайта не отвечает, все права принадлежат их создателям. Если вы нашли то, что искали, отблагодарите авторов - поделитесь ссылкой в социальных сетях, а наш сайт добавьте в закладки.

Презентации » Технология » Запамятовуючі пристрої СО (Заняття 7. 3)

Оцените!

Оцените презентацию от 1 до 5 баллов!

- Тип файла:ppt / pptx (powerpoint)

- Всего слайдов:30 слайдов

- Для класса:1,2,3,4,5,6,7,8,9,10,11

- Размер файла:311.50 kB

- Просмотров:43

- Скачиваний:0

- Автор:неизвестен

Слайды и текст к этой презентации:

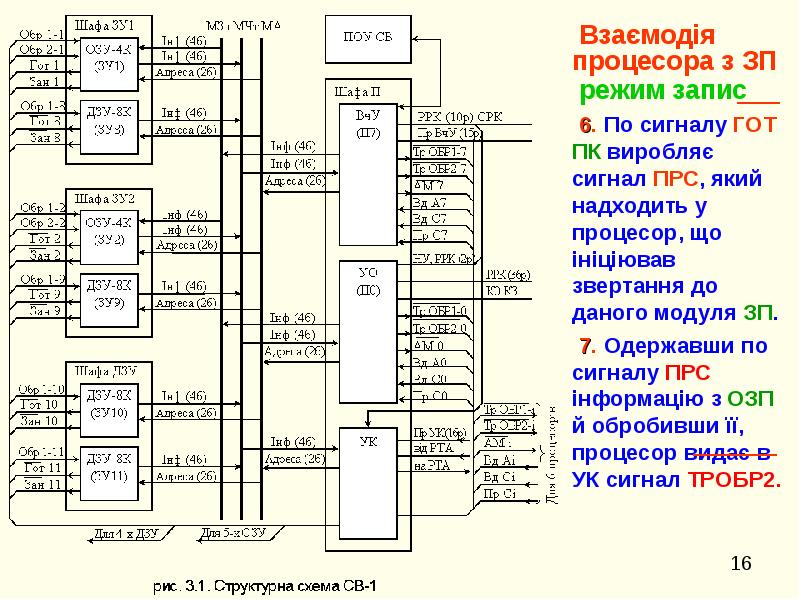

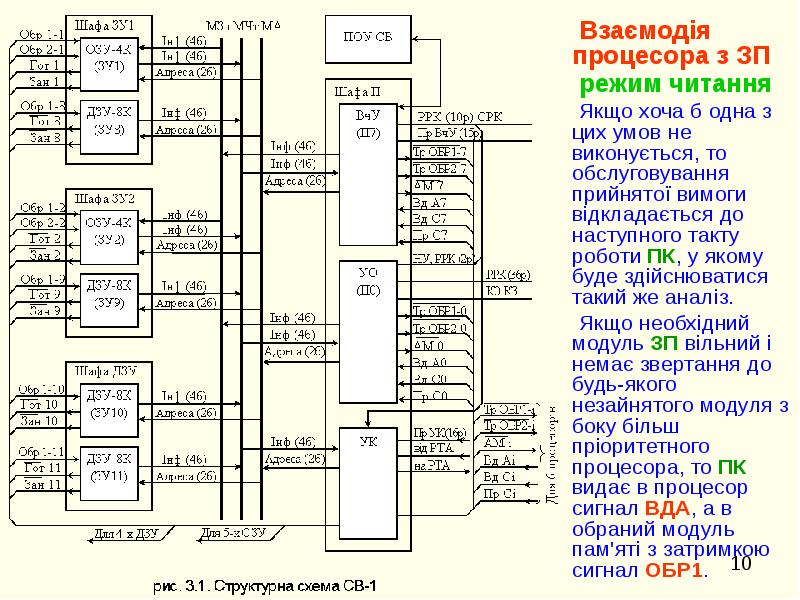

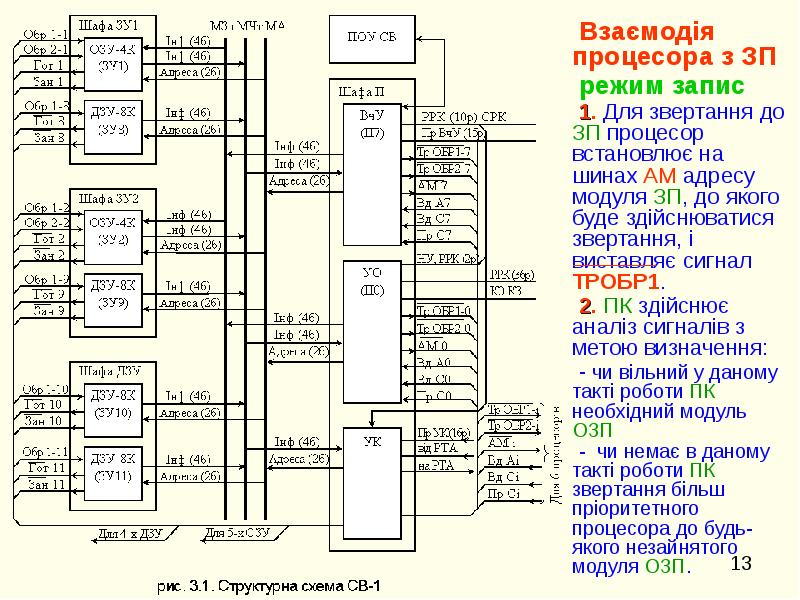

№5 слайд

Содержание слайда: ПК в “СВ-1” виконує в основному функції пріоритетного обслуговування заявок ПО й ОбП до запам'ятовуючих пристроїв. ПК має 8 рангів пріоритетів для підключення процесорів. В “CB-1” ПО підключено до старшого - 0-го пріоритету, а ОбП до молодшого – 7‑го пріоритету. Зв'язки між ЗП і процесорами здійснюються за допомогою ВМК, що складається з магістралі запису МЗп, магістралі читання МЧт і магістралі адреси МА. Причому:

ПК в “СВ-1” виконує в основному функції пріоритетного обслуговування заявок ПО й ОбП до запам'ятовуючих пристроїв. ПК має 8 рангів пріоритетів для підключення процесорів. В “CB-1” ПО підключено до старшого - 0-го пріоритету, а ОбП до молодшого – 7‑го пріоритету. Зв'язки між ЗП і процесорами здійснюються за допомогою ВМК, що складається з магістралі запису МЗп, магістралі читання МЧт і магістралі адреси МА. Причому:

МЗп передає 36-розрядне слово від процесора до ЗП;

МЧт передає 36-розрядне слово від ЗП до процесора, а також молодший байт із контрольним розрядом від регістрів ПК до процесорів;

МА передає 18-розрядну адресу комірки від процесора до модуля ЗП. Крім того, 12 молодших розрядів МА використовуються для передачі інформації і команди з процесора на регістри ПК.

№6 слайд

Содержание слайда: По частині керування внутрішнім обміном ПК з'єднаний з кожним процесором і модулем ЗП індивідуальними шинами. Від кожного процесора ПК одержує сигнали ТРЕБОВАНИЕ ОБРАЩЕНИЯ 1 (ТРОБР1), ТРЕБОВАНИЕ ОБРАЩЕНИЯ 2 (ТРОБР2), 4-розрядну адресу модуля ЗП (АМ), а видає сигнали ВЫДАЧА АДРЕСА (ВДА), ВЫДАЧА СЛОВА (ВДС) і ПРИЕМ СЛОВА (ПРС).

По частині керування внутрішнім обміном ПК з'єднаний з кожним процесором і модулем ЗП індивідуальними шинами. Від кожного процесора ПК одержує сигнали ТРЕБОВАНИЕ ОБРАЩЕНИЯ 1 (ТРОБР1), ТРЕБОВАНИЕ ОБРАЩЕНИЯ 2 (ТРОБР2), 4-розрядну адресу модуля ЗП (АМ), а видає сигнали ВЫДАЧА АДРЕСА (ВДА), ВЫДАЧА СЛОВА (ВДС) і ПРИЕМ СЛОВА (ПРС).

Від кожного модуля ЗП ПК одержує сигнали ГОТОВНОСТЬ (ГОТ) і ЗАНЯТОСТЬ (ЗАН), а видає сигнали ОБРАЩЕНИЕ 1 (ОБР1) і ОБРАЩЕНИЕ 2 (ОБР2) (тільки для ОЗП). Причому, сигнали ТРОБР1, АМ, ТРОБР2, ГОТ, ЗАН мають низький рівень. Інші сигнали мають високий рівень. За інформацією ПК з'єднаний з МА в обсязі 12-ти молодших розрядів і з МЧт в обсязі одного молодшого байта.

№7 слайд

Содержание слайда: Призначення сигналів:

Призначення сигналів:

ТРОБР1 - подається в ПК процесором бажаючим звернутися к модулеві ЗП, номер якого зазначений в АМ;

ТРОБР2 - подається в ПК процесором, через деякий час після сигналу ПРС, якщо даний процесор робить запис у ЗП;

ВДА - видається ПК тому процесорові, вимога на звертання 1 (ТРОБР1), якого задоволена. Сигнал дозволяє видачу адреси в МА;

ВДС - видається ПК тому процесорові, вимога на звертання 2, (ТРОБР2), якого задоволена. Сигнал дозволяє видати слово в МЗп;

ПРС - видається ПК тому процесорові, вимога на звертання 1, (ТРОБР1), якого задоволена. Сигнал дозволяє прийом слова з МЧт;

№8 слайд

Содержание слайда: ОБР1 - видається ПК незайнятому модулеві ЗП, у випадку якщо вимога на звертання 1 від даного процесора задоволена. Сигнал включає в роботу даний модуль ЗП;

ОБР1 - видається ПК незайнятому модулеві ЗП, у випадку якщо вимога на звертання 1 від даного процесора задоволена. Сигнал включає в роботу даний модуль ЗП;

ОБР2 - видається ПК тому модулеві ЗП, що одержав сигнал ОБР1 і ознаку запису. Сигнал керує режимом запису обраного модуля ЗП;

ГОТ - видається модулем ЗП через 1,2 мкс після приходу сигналу ОБР1. Сигнал використовується для визначення процесора, до якого адресується зчитане слово;

ЗАН - видається модулем ЗП через 80 нс після приходу сигналу ОБР1. Тривалість його у межах 0,66 мкс і 1,3 мкс (при читанні). Сигнал служить для аналізу стану зайнятості модуля ЗП, до якого адресується вимога на звертання.

№9 слайд

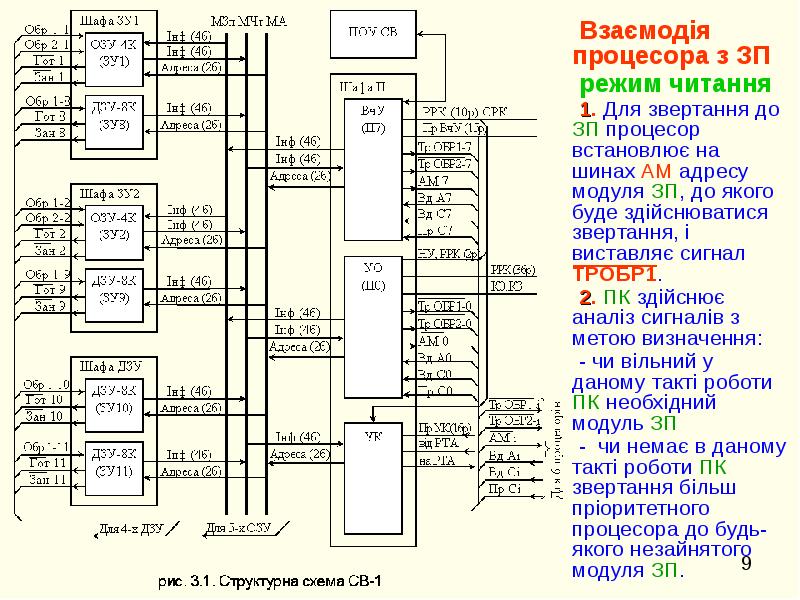

Содержание слайда: Взаємодія процесора з ЗП

Взаємодія процесора з ЗП

режим читання

1. Для звертання до ЗП процесор встановлює на шинах АМ адресу модуля ЗП, до якого буде здійснюватися звертання, і виставляє сигнал ТРОБР1.

2. ПК здійснює аналіз сигналів з метою визначення:

- чи вільний у даному такті роботи ПК необхідний модуль ЗП

- чи немає в даному такті роботи ПК звертання більш пріоритетного процесора до будь-якого незайнятого модуля ЗП.

№10 слайд

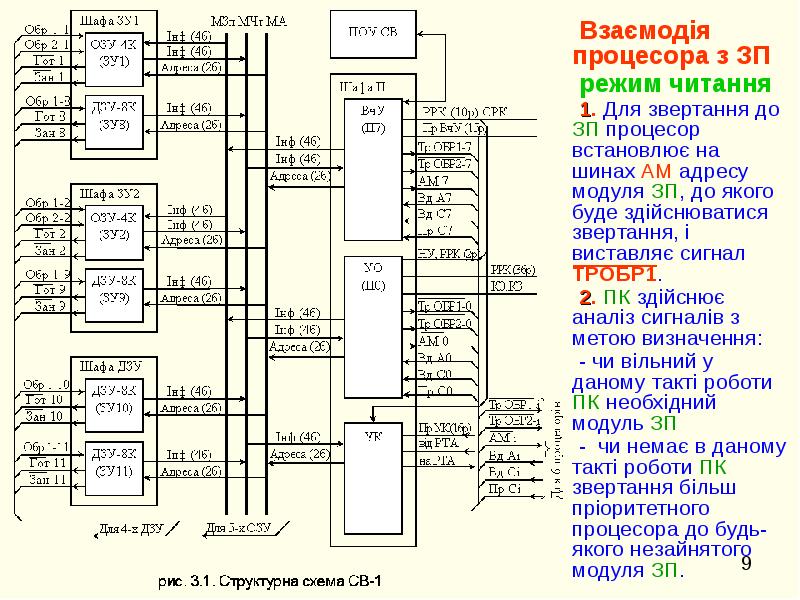

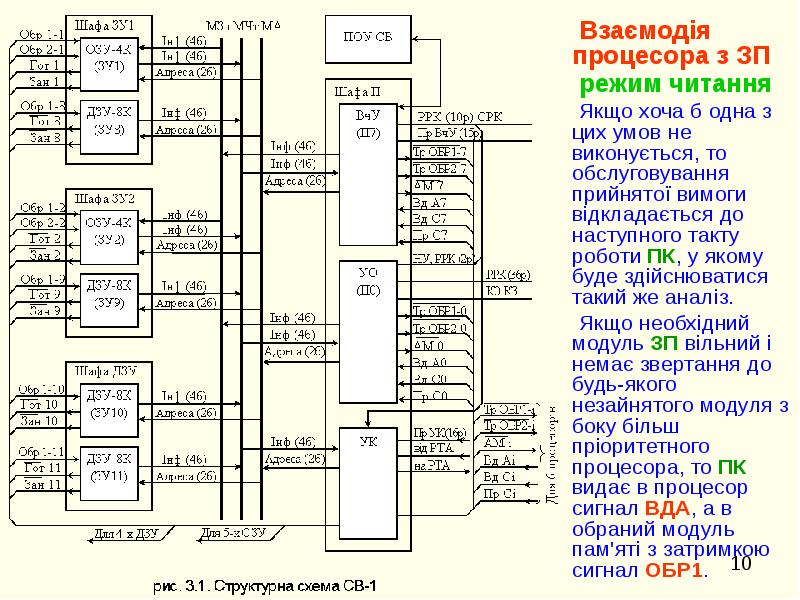

Содержание слайда: Взаємодія процесора з ЗП

Взаємодія процесора з ЗП

режим читання

Якщо хоча б одна з цих умов не виконується, то обслуговування прийнятої вимоги відкладається до наступного такту роботи ПК, у якому буде здійснюватися такий же аналіз.

Якщо необхідний модуль ЗП вільний і немає звертання до будь-якого незайнятого модуля з боку більш пріоритетного процесора, то ПК видає в процесор сигнал ВДА, а в обраний модуль пам'яті з затримкою сигнал ОБР1.

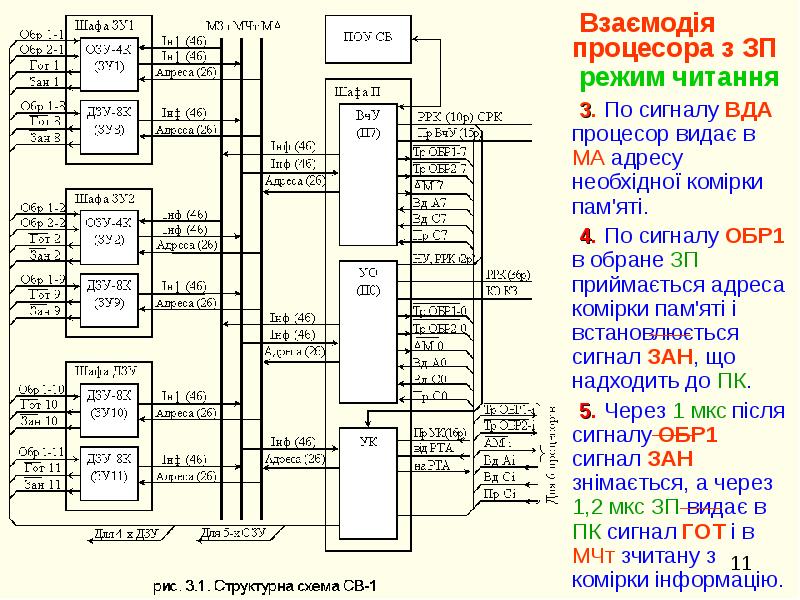

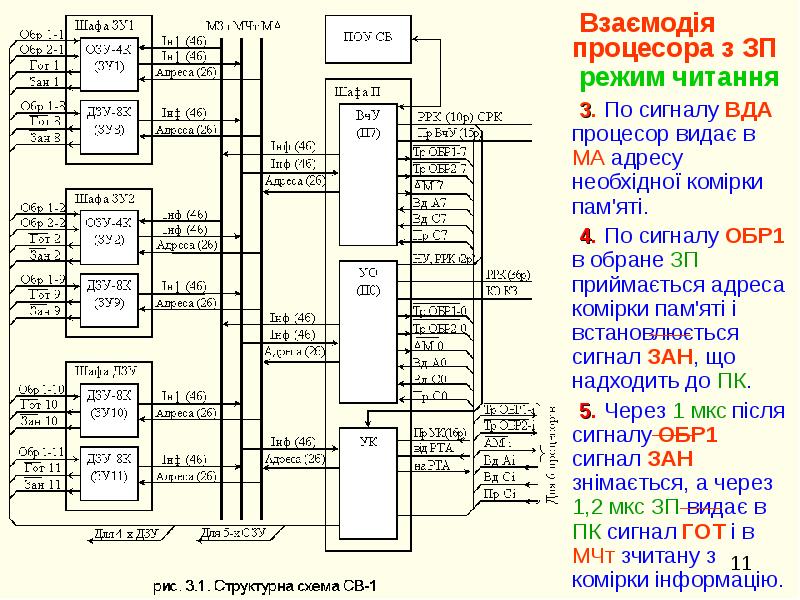

№11 слайд

Содержание слайда: Взаємодія процесора з ЗП

Взаємодія процесора з ЗП

режим читання

3. По сигналу ВДА процесор видає в МА адресу необхідної комірки пам'яті.

4. По сигналу ОБР1 в обране ЗП приймається адреса комірки пам'яті і встановлюється сигнал ЗАН, що надходить до ПК.

5. Через 1 мкс після сигналу ОБР1 сигнал ЗАН знімається, а через 1,2 мкс ЗП видає в ПК сигнал ГОТ і в МЧт зчитану з комірки інформацію.

№12 слайд

Содержание слайда: Взаємодія процесора з ЗП

Взаємодія процесора з ЗП

режим читання

6. По сигналу ГОТ ПК виробляє сигнал ПРС, який надходить у процесор, що ініціював звертання до даного модуля ЗП.

7. По сигналу ПРС здійснюється прийом до процесора зчитаной з ЗП інформації.

На цьому цикл читання завершується.

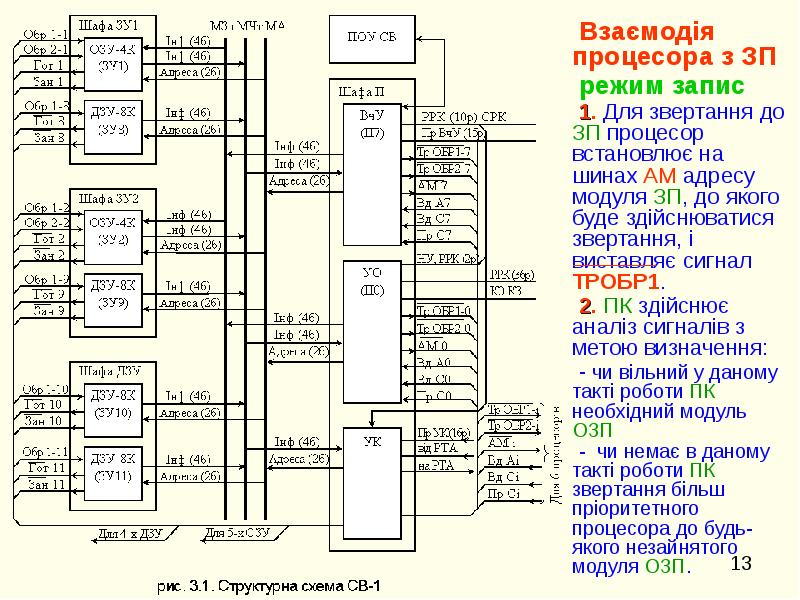

№13 слайд

Содержание слайда: Взаємодія процесора з ЗП

Взаємодія процесора з ЗП

режим запис

1. Для звертання до ЗП процесор встановлює на шинах АМ адресу модуля ЗП, до якого буде здійснюватися звертання, і виставляє сигнал ТРОБР1.

2. ПК здійснює аналіз сигналів з метою визначення:

- чи вільний у даному такті роботи ПК необхідний модуль ОЗП

- чи немає в даному такті роботи ПК звертання більш пріоритетного процесора до будь-якого незайнятого модуля ОЗП.

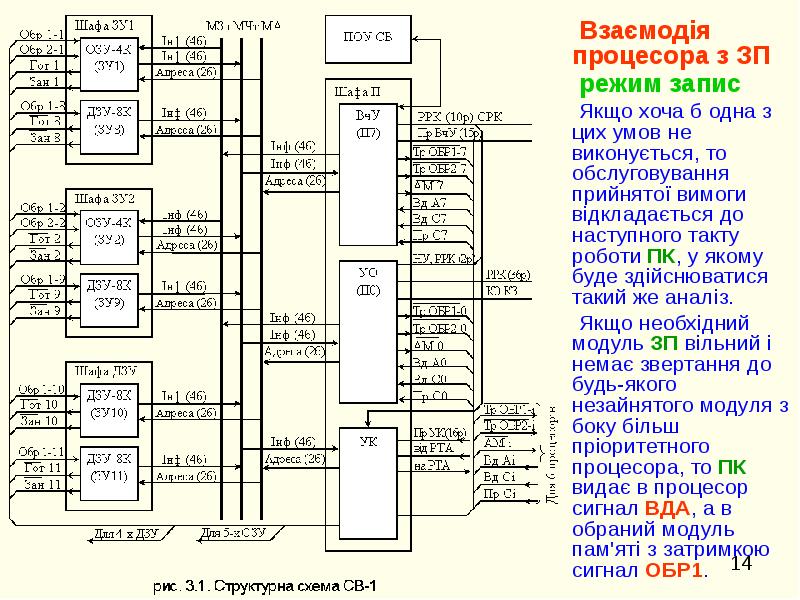

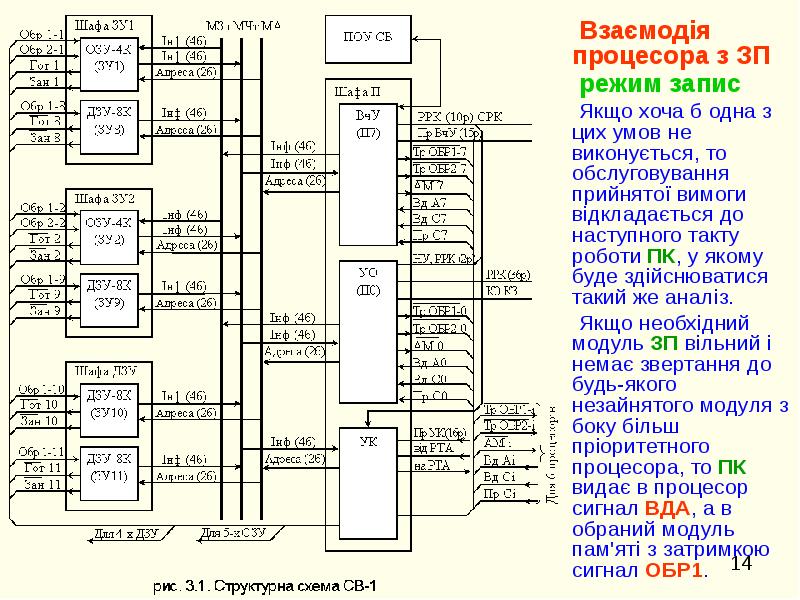

№14 слайд

Содержание слайда: Взаємодія процесора з ЗП

Взаємодія процесора з ЗП

режим запис

Якщо хоча б одна з цих умов не виконується, то обслуговування прийнятої вимоги відкладається до наступного такту роботи ПК, у якому буде здійснюватися такий же аналіз.

Якщо необхідний модуль ЗП вільний і немає звертання до будь-якого незайнятого модуля з боку більш пріоритетного процесора, то ПК видає в процесор сигнал ВДА, а в обраний модуль пам'яті з затримкою сигнал ОБР1.

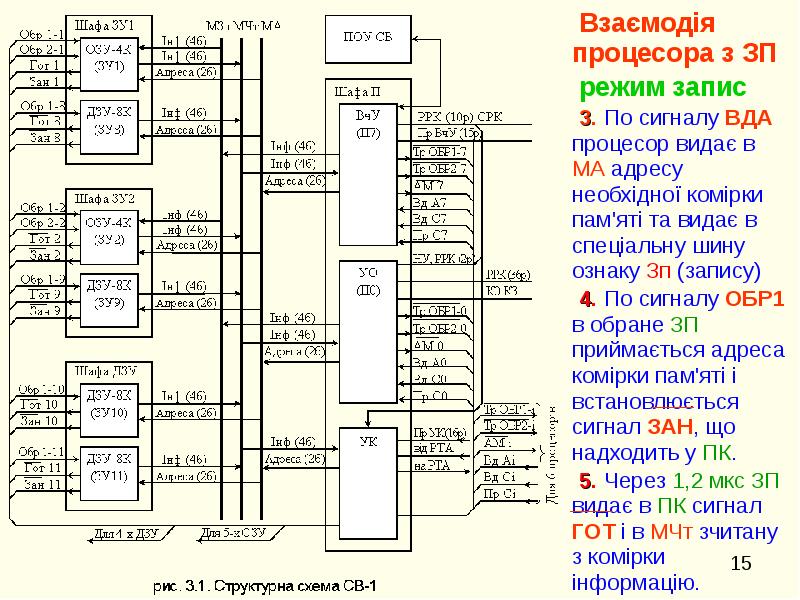

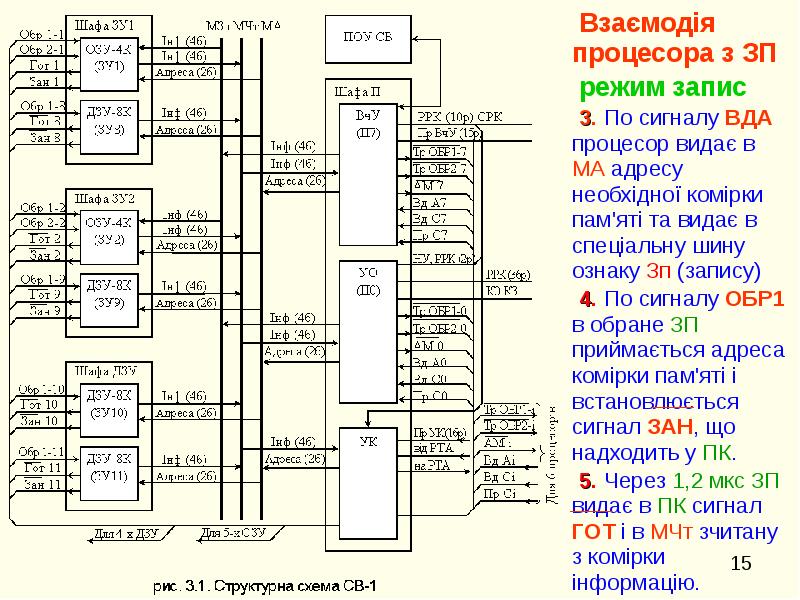

№15 слайд

Содержание слайда: Взаємодія процесора з ЗП

Взаємодія процесора з ЗП

режим запис

3. По сигналу ВДА процесор видає в МА адресу необхідної комірки пам'яті та видає в спеціальну шину ознаку Зп (запису)

4. По сигналу ОБР1 в обране ЗП приймається адреса комірки пам'яті і встановлюється сигнал ЗАН, що надходить у ПК.

5. Через 1,2 мкс ЗП видає в ПК сигнал ГОТ і в МЧт зчитану з комірки інформацію.

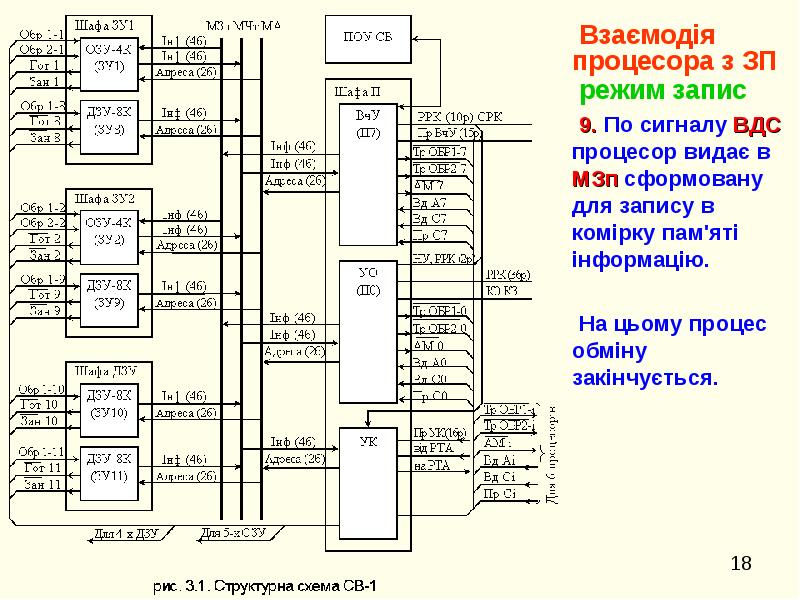

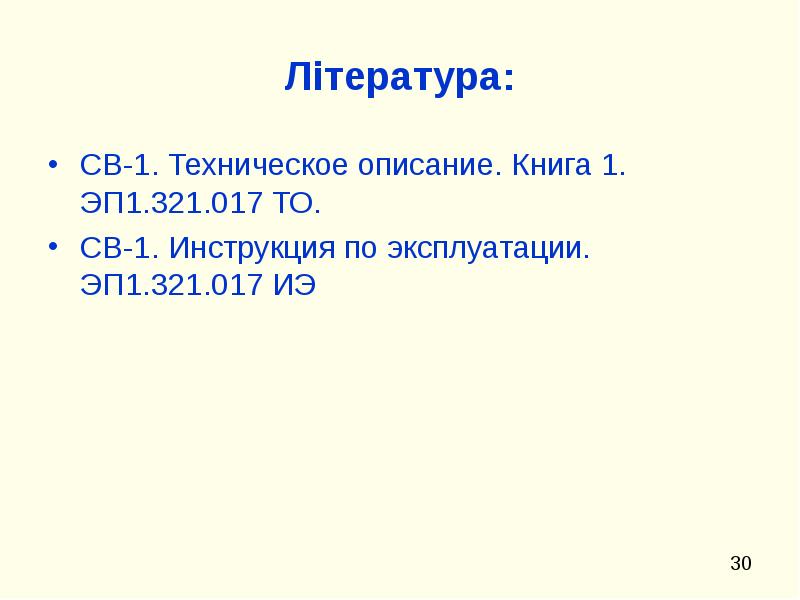

№17 слайд

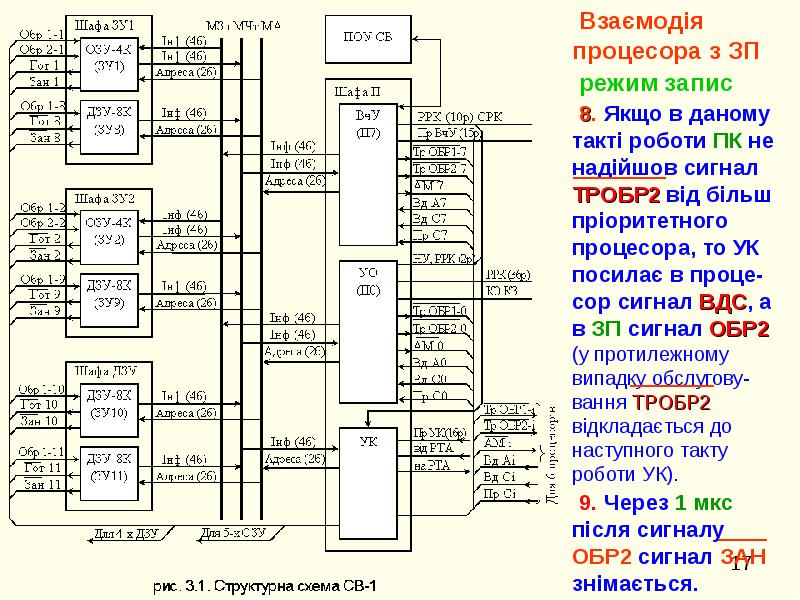

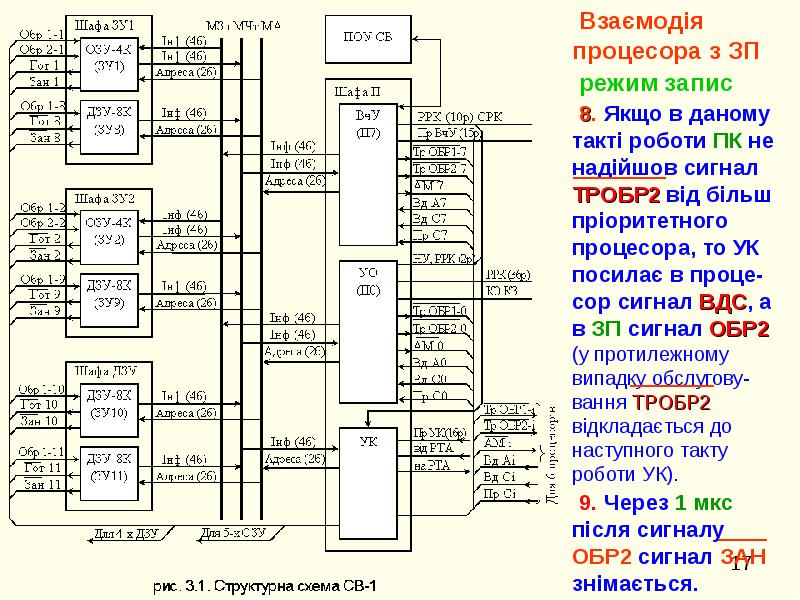

Содержание слайда: Взаємодія процесора з ЗП

Взаємодія процесора з ЗП

режим запис

8. Якщо в даному такті роботи ПК не надійшов сигнал ТPOБP2 від більш пріоритетного процесора, то УК посилає в проце-сор сигнал ВДС, а в ЗП сигнал ОБР2 (у протилежному випадку обслугову-вання ТРОБР2 відкладається до наступного такту роботи УК).

9. Через 1 мкс після сигналу ОБР2 сигнал ЗАН знімається.

№19 слайд

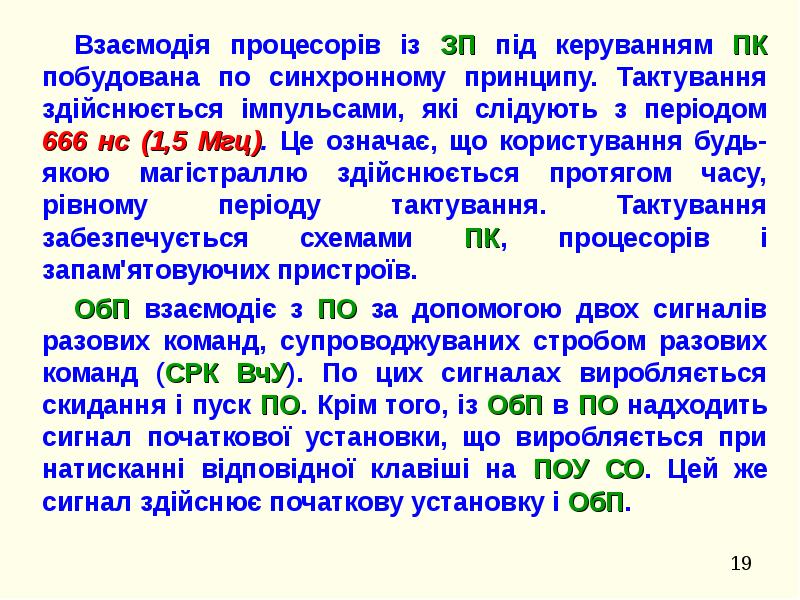

Содержание слайда: Взаємодія процесорів із ЗП під керуванням ПК побудована по синхронному принципу. Тактування здійснюється імпульсами, які слідують з періодом 666 нс (1,5 Мгц). Це означає, що користування будь-якою магістраллю здійснюється протягом часу, рівному періоду тактування. Тактування забезпечується схемами ПК, процесорів і запам'ятовуючих пристроїв.

Взаємодія процесорів із ЗП під керуванням ПК побудована по синхронному принципу. Тактування здійснюється імпульсами, які слідують з періодом 666 нс (1,5 Мгц). Це означає, що користування будь-якою магістраллю здійснюється протягом часу, рівному періоду тактування. Тактування забезпечується схемами ПК, процесорів і запам'ятовуючих пристроїв.

ОбП взаємодіє з ПО за допомогою двох сигналів разових команд, супроводжуваних стробом разових команд (СРК ВчУ). По цих сигналах виробляється скидання і пуск ПО. Крім того, із ОбП в ПО надходить сигнал початкової установки, що виробляється при натисканні відповідної клавіші на ПОУ СО. Цей же сигнал здійснює початкову установку і ОбП.

№21 слайд

Содержание слайда: Крім сигналів функціональної взаємодії ПК, ПО і ОбП зв'язані один з одним єдиною синхронізацією. Генератор синхроімпульсів, розташований в ПК, виробляє 8 сінхросерій:

Крім сигналів функціональної взаємодії ПК, ПО і ОбП зв'язані один з одним єдиною синхронізацією. Генератор синхроімпульсів, розташований в ПК, виробляє 8 сінхросерій:

СИ1-СИ4, які слідують з періодом 666 нс, причому, закінчення попереднього синхроімпульсу збігається з початком наступних;

СИС1 - СИС4, що мають те жe параметри, що і СИ1 - СИ4, але зрушені щодо останніх на 82 нс.

Синхроімпульси через елементи узгодження, конструктивно розташовувані в КРС-3, видаються на ПО і ОбП

№22 слайд

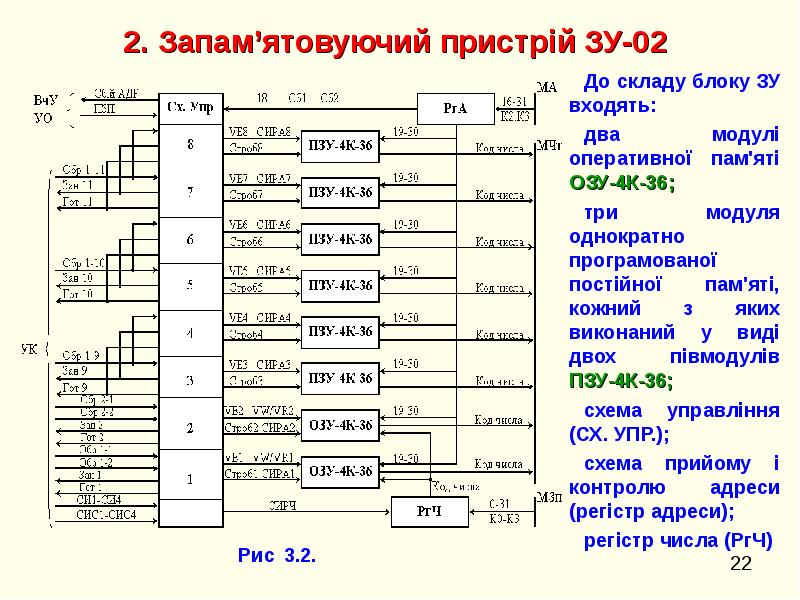

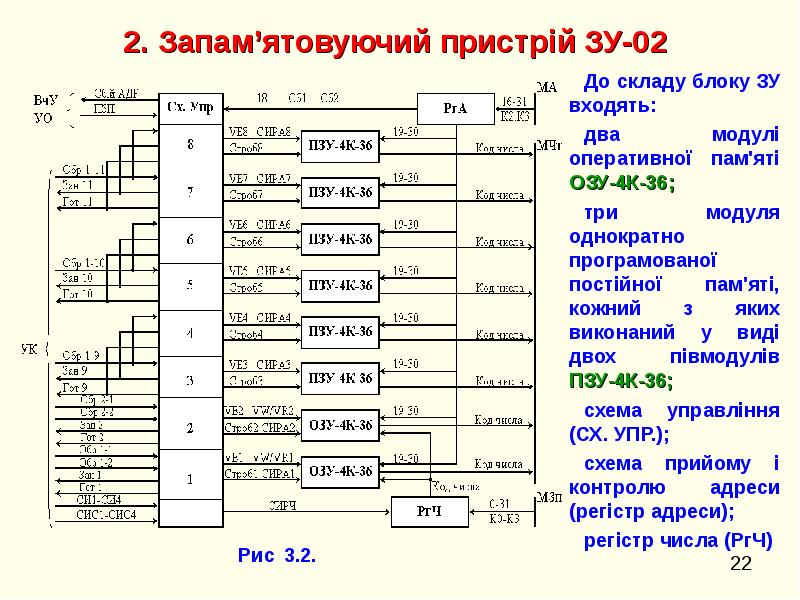

Содержание слайда: До складу блоку ЗУ входять:

До складу блоку ЗУ входять:

два модулі оперативної пам'яті ОЗУ-4К-36;

три модуля однократно програмованої постійної пам'яті, кожний з яких виконаний у виді двох півмодулів ПЗУ-4К-36;

схема управління (СХ. УПР.);

схема прийому і контролю адреси (регістр адреси);

регістр числа (РгЧ)

№23 слайд

Содержание слайда: Схема управління (СХ. УПР.) у залежності від прийнятих від ПК і процесорів сигналів керування робить підключення робочого модуля і формує необхідні для його роботи сигнали.

Схема управління (СХ. УПР.) у залежності від прийнятих від ПК і процесорів сигналів керування робить підключення робочого модуля і формує необхідні для його роботи сигнали.

Схема прийому і контролю адреси (РА) здійснює прийом, побайтний контроль коду адреси на парність і передачу його в модулі пам'яті.

Регістр числа (РгЧ) призначений для прийому коду числа від процесора і збереження його до моменту запису в заданий модуль ОЗП.

Модулі оперативної пам'яті дозволяють приймати, зберігати і видавати до 4096 36-розрядних чисел кожний.

Півмодулі однократно програмованої пам'яті зберігають і видають у процесори до 4096 36-розрядних чисел, записаних на спеціальному програматоре в процесі виготовлення.

№24 слайд

Содержание слайда: Усі модулі блоку ЗП мають наскрізну фізичну нумерацію від 1 до 8. Звертання до кожного конкретного модуля здійснюється відповідно до привласненого йому математичного номеру. При цьому математичні номери модулів ОЗП відповідають їх фізичним номерам, а півмодулям ПЗП привласнені наступні математичні номери: третьому і четвертому - номер 9; п'ятому і шостому - номер 10, сьомому і восьмому - номер 11. Схема управління має як загальне обладнання, необхідне для організації роботи всього блоку, так і індивідуальне обладнання, що формує сигнали керування для кожного модуля ОЗП і ПЗП по незалежній програмі. Синхронізація роботи вузлів схеми управління здійснюється за допомогою синхроімпульсів СИ1—СИ4, що надходять у блок ЗП від ПК .

Усі модулі блоку ЗП мають наскрізну фізичну нумерацію від 1 до 8. Звертання до кожного конкретного модуля здійснюється відповідно до привласненого йому математичного номеру. При цьому математичні номери модулів ОЗП відповідають їх фізичним номерам, а півмодулям ПЗП привласнені наступні математичні номери: третьому і четвертому - номер 9; п'ятому і шостому - номер 10, сьомому і восьмому - номер 11. Схема управління має як загальне обладнання, необхідне для організації роботи всього блоку, так і індивідуальне обладнання, що формує сигнали керування для кожного модуля ОЗП і ПЗП по незалежній програмі. Синхронізація роботи вузлів схеми управління здійснюється за допомогою синхроімпульсів СИ1—СИ4, що надходять у блок ЗП від ПК .

№25 слайд

Содержание слайда: Модулі ПЗП можуть працювати в складі СВ-4 тільки в режимі «Читання», а модулі ОЗУ - в одному з двох режимів: «Читання» - зчитування по заданій адресі раніше записаної інформації або «Модифікований запис» - зчитування і видача в МЧт раніше записаної інформації і запис по цій же адресі нової інформації.

Модулі ПЗП можуть працювати в складі СВ-4 тільки в режимі «Читання», а модулі ОЗУ - в одному з двох режимів: «Читання» - зчитування по заданій адресі раніше записаної інформації або «Модифікований запис» - зчитування і видача в МЧт раніше записаної інформації і запис по цій же адресі нової інформації.

Через те що схеми управління модулів ОЗП і ПЗП однакові, розглянемо роботу ЗП в режимі «Читання» на прикладі дев'ятого модуля ПЗП.

Від ПК надходить сигнал звертання ОБР. 1—9 на входи схем управління третього і четвертого модулів ПЗП. Одночасно від процесора через магістраль адреси МА на РА приймається код адреси комірки в модулі в складі 16 інформаційних (16—31 розряди) і двох контрольних (К2, КЗ) розрядів.

№26 слайд

Содержание слайда: Розряди з 19-го по 30-й однозначно визначають номер комірки в модулі ОЗП або півмодулі ПЗП, а 18-й розряд — номер півмодуля ПЗП. Нехай значення 18-го розряду дорівнює «1». Тоді по сигналу ОБР. 1—9 у СХ. УПР. запуститься схема управління четвертого півмодуля ПЗП і послідовно в часі сформуються сигнали: СИРА-4; ЗАН. 9; VЕ-4; ГОТ. 9; СТРОБ-4, що мають строго визначені тривалості і часові положення. По синхроімпульсу СИРА‑4 12-розрядний код адреси заноситься з РА в четвертий модуль і запам'ятовується в ньому, оскільки інформація в РА зберігається тільки на час присутності сигналу ОБР. 1. Сигнал дозволу вибірки VЕ-4 разом з кодом адреси забезпечує зчитування інформації з визначеної комірки пам'яті. Сигнал ГОТ. 9 повідомляє ПК про готовність модуля видати зчитану інформацію в МЧт. Зчитана інформація стробуется в часі сигналом СТРОБ-4 і у виді 36-розрядного коду видається в МЧт.

Розряди з 19-го по 30-й однозначно визначають номер комірки в модулі ОЗП або півмодулі ПЗП, а 18-й розряд — номер півмодуля ПЗП. Нехай значення 18-го розряду дорівнює «1». Тоді по сигналу ОБР. 1—9 у СХ. УПР. запуститься схема управління четвертого півмодуля ПЗП і послідовно в часі сформуються сигнали: СИРА-4; ЗАН. 9; VЕ-4; ГОТ. 9; СТРОБ-4, що мають строго визначені тривалості і часові положення. По синхроімпульсу СИРА‑4 12-розрядний код адреси заноситься з РА в четвертий модуль і запам'ятовується в ньому, оскільки інформація в РА зберігається тільки на час присутності сигналу ОБР. 1. Сигнал дозволу вибірки VЕ-4 разом з кодом адреси забезпечує зчитування інформації з визначеної комірки пам'яті. Сигнал ГОТ. 9 повідомляє ПК про готовність модуля видати зчитану інформацію в МЧт. Зчитана інформація стробуется в часі сигналом СТРОБ-4 і у виді 36-розрядного коду видається в МЧт.

№27 слайд

Содержание слайда: Сигнал зайнятості модуля (ЗАН. 9) установлюється по передньому фронту сигналу звертання ОБР. 1—9 і скидається по задньому фронту сигналу VЕ-4.

Сигнал зайнятості модуля (ЗАН. 9) установлюється по передньому фронту сигналу звертання ОБР. 1—9 і скидається по задньому фронту сигналу VЕ-4.

Схема управління (СХ. УПР.) формує узагальнений сигнал збою адреси ЗБІЙ АДР., якщо від РА надійде сигнал Сб.1 або Сб.2 при виявленні помилки в першому або другому байті прийнятого коду адреси відповідно.

У режимі «Модифікований запис» від процесора на вхід схеми управління надходить ознаку запису ПЗп одночасно із сигналом ОБР. 1. Роботу модуля ОЗП в цьому режимі можна розділити на дві фази — читання інформації з комірки і запис нової інформації в цю комірку. Читання інформації з комірки ОЗП здійснюється так само, як і з комірки ПЗП, за винятком того, що сигнал зайнятості модуля по закінченні читання не скидається.

№28 слайд

Содержание слайда: Після підготовки нової інформації для запису від КК на СХ. УПР. надходить сигнал звертання на запис, наприклад, ОБР. 2—1, а від процесора — 36-розрядний код числа через магістраль МЗп. По сигналу ОБР. 2-1 схема управління формує сигнали СИРЧ; VЕ-1; VW/VR1. По синхроімпульсі СИРЧ код записуваного числа заноситься в регістр РгЧ. Сигнал VЕ-1, як і в режимі читання, дозволяє вибірку комірки пам'яті по встановленій адресі. Ознака запису/читання VW/VR1 переводить комірку в режим запису, і інформаційне слово з РгЧ переписується в комірку пам'яті. Одночасно скидається сигнал зайнятості модуля ЗАН.-1. У режимі «Модифікований запис» формування сигналів, керуючих записом, блокується при виявленні помилки в коді адреси, тобто при наявності сигналу Сб. 1 або Сб. 2.

Після підготовки нової інформації для запису від КК на СХ. УПР. надходить сигнал звертання на запис, наприклад, ОБР. 2—1, а від процесора — 36-розрядний код числа через магістраль МЗп. По сигналу ОБР. 2-1 схема управління формує сигнали СИРЧ; VЕ-1; VW/VR1. По синхроімпульсі СИРЧ код записуваного числа заноситься в регістр РгЧ. Сигнал VЕ-1, як і в режимі читання, дозволяє вибірку комірки пам'яті по встановленій адресі. Ознака запису/читання VW/VR1 переводить комірку в режим запису, і інформаційне слово з РгЧ переписується в комірку пам'яті. Одночасно скидається сигнал зайнятості модуля ЗАН.-1. У режимі «Модифікований запис» формування сигналів, керуючих записом, блокується при виявленні помилки в коді адреси, тобто при наявності сигналу Сб. 1 або Сб. 2.

№29 слайд

Содержание слайда: Після підготовки нової інформації для запису від КК на СХ. УПР. надходить сигнал звертання на запис, наприклад, ОБР. 2—1, а від процесора — 36-розрядний код числа через магістраль МЗп. По сигналу ОБР. 2-1 схема управління формує сигнали СИРЧ; VЕ-1; VW/VR1. По синхроімпульсі СИРЧ код записуваного числа заноситься в регістр РгЧ. Сигнал VЕ-1, як і в режимі читання, дозволяє вибірку комірки пам'яті по встановленій адресі. Ознака запису/читання VW/VR1 переводить комірку в режим запису, і інформаційне слово з РгЧ переписується в комірку пам'яті. Одночасно скидається сигнал зайнятості модуля ЗАН.-1. У режимі «Модифікований запис» формування сигналів, керуючих записом, блокується при виявленні помилки в коді адреси, тобто при наявності сигналу Сб. 1 або Сб. 2.

Після підготовки нової інформації для запису від КК на СХ. УПР. надходить сигнал звертання на запис, наприклад, ОБР. 2—1, а від процесора — 36-розрядний код числа через магістраль МЗп. По сигналу ОБР. 2-1 схема управління формує сигнали СИРЧ; VЕ-1; VW/VR1. По синхроімпульсі СИРЧ код записуваного числа заноситься в регістр РгЧ. Сигнал VЕ-1, як і в режимі читання, дозволяє вибірку комірки пам'яті по встановленій адресі. Ознака запису/читання VW/VR1 переводить комірку в режим запису, і інформаційне слово з РгЧ переписується в комірку пам'яті. Одночасно скидається сигнал зайнятості модуля ЗАН.-1. У режимі «Модифікований запис» формування сигналів, керуючих записом, блокується при виявленні помилки в коді адреси, тобто при наявності сигналу Сб. 1 або Сб. 2.

Сигнали звертання на читання (ОБР. 1) у різні модулі пам'яті можуть подаватися через час не менш 600 нс. Одночасна видача сигналів ОБР. 1 і ОБР. 2 можлива тільки в різні модулі пам'яті.

Скачать все slide презентации Запамятовуючі пристрої СО (Заняття 7. 3) одним архивом:

Похожие презентации

-

Апаратура обчислювальних засобів. Оперативний запамятовуючий пристрій (Заняття 7. 7)

Апаратура обчислювальних засобів. Оперативний запамятовуючий пристрій (Заняття 7. 7) -

Радіостанції ОРС та антенні пристрої. (Практичне заняття 3. 2)

Радіостанції ОРС та антенні пристрої. (Практичне заняття 3. 2) -

Пристрій керування каналом (Заняття 7. 9)

Пристрій керування каналом (Заняття 7. 9) -

Пристрої цифрової обробки радіолокаційних сигналів (заняття 2. 5)

Пристрої цифрової обробки радіолокаційних сигналів (заняття 2. 5) -

Індикаторні пристрої (заняття 2. 6)

Індикаторні пристрої (заняття 2. 6) -

Загальні відомості і принципи дії фідерних пристроїв (Заняття 4. 1)

Загальні відомості і принципи дії фідерних пристроїв (Заняття 4. 1) -

Апаратура обчислювальних засобів. Пристрій обміну інформацією (Заняття 7. 20)

Апаратура обчислювальних засобів. Пристрій обміну інформацією (Заняття 7. 20) -

Апаратура обчислювальних засобів. Контроль функціонування пристрою обміну інформації (Заняття 7. 21)

Апаратура обчислювальних засобів. Контроль функціонування пристрою обміну інформації (Заняття 7. 21) -

Апаратура обчислювальних засобів. Пристрій управління висотомірами (Заняття 7. 22)

Апаратура обчислювальних засобів. Пристрій управління висотомірами (Заняття 7. 22) -

Апаратура обчислювальних засобів. Контроль функціонування пристрою управління висотомірами (Заняття 7. 23)

Апаратура обчислювальних засобів. Контроль функціонування пристрою управління висотомірами (Заняття 7. 23)