Оцените презентацию от 1 до 5 баллов!

Тип файла:

ppt / pptx (powerpoint)

Всего слайдов:

45 слайдов

Для класса:

1,2,3,4,5,6,7,8,9,10,11

Размер файла:

5.54 MB

Просмотров:

96

Скачиваний:

2

Автор:

неизвестен

Слайды и текст к этой презентации:

№1 слайд

Содержание слайда: Организация системы ввода вывода

Логическая организация СВВ, аппаратная организация СВВ, контроллеры: параллельного В-В, последовательного В-В, ПДП. Микросхемы UART, PIO.

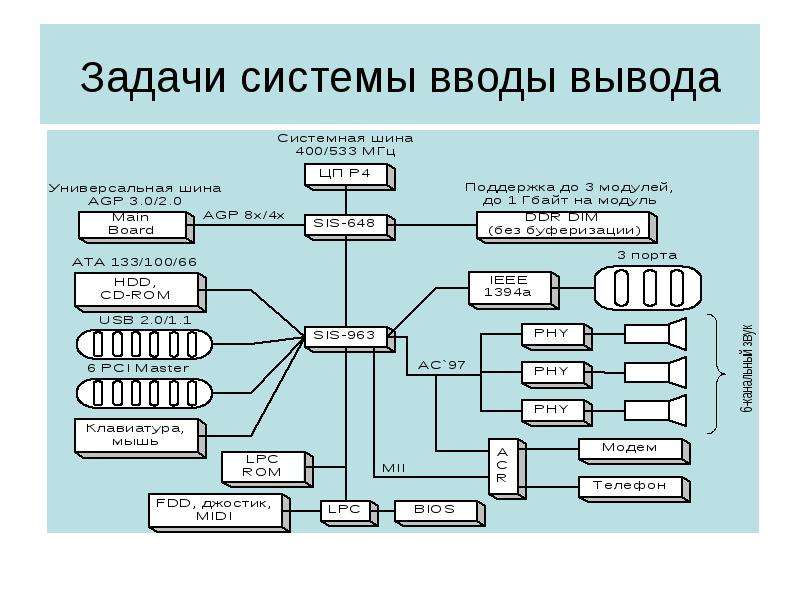

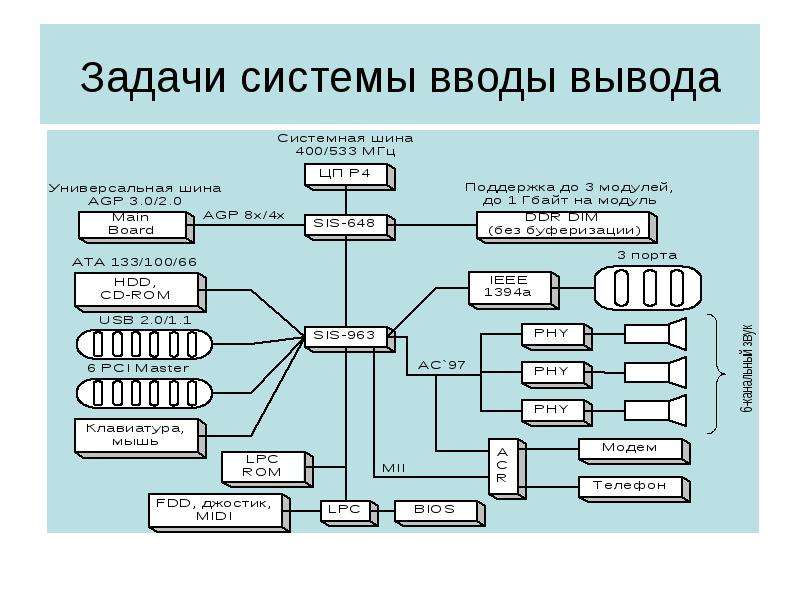

№2 слайд

Содержание слайда: Задачи системы вводы вывода

№3 слайд

Содержание слайда: Глобальные задачи СВВ

Обеспечение максимальной производительности вычислительной системы.

Возможность изменения конфигурации периферийных устройств (ПУ).

Возможность модифицировать ПУ , не изменяя ядро системы.

№4 слайд

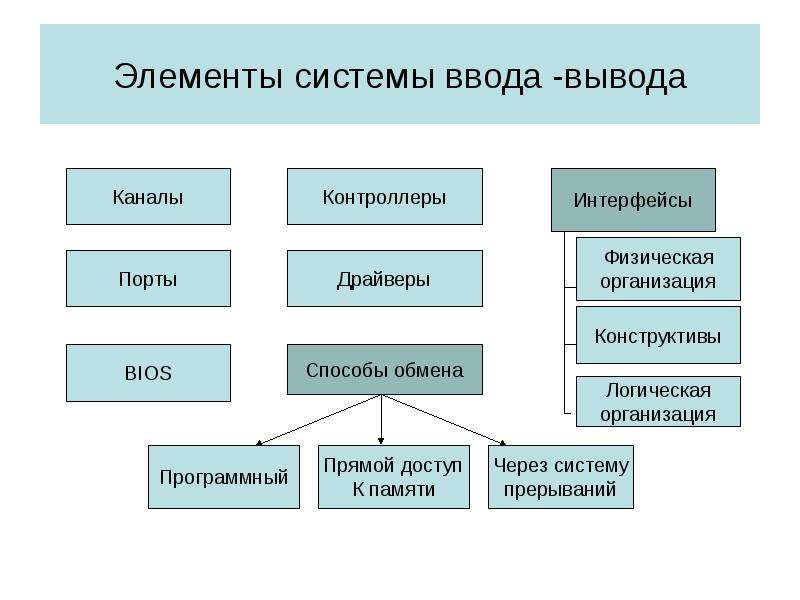

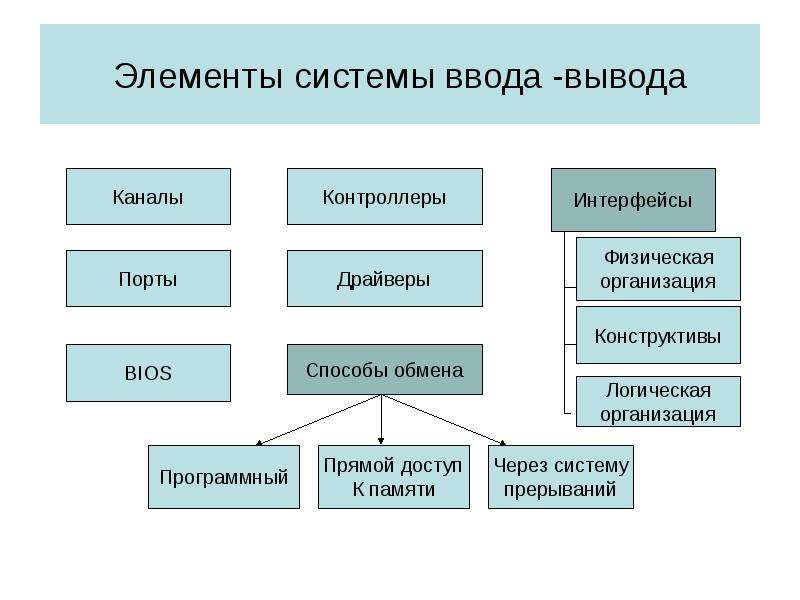

Содержание слайда: Элементы системы ввода -вывода

№5 слайд

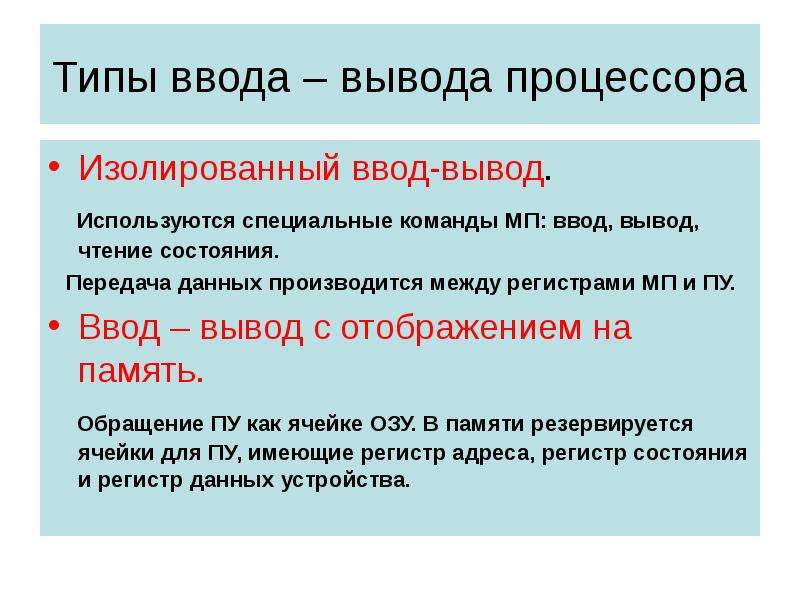

Содержание слайда: Типы ввода – вывода процессора

Изолированный ввод-вывод.

Используются специальные команды МП: ввод, вывод, чтение состояния.

Передача данных производится между регистрами МП и ПУ.

Ввод – вывод с отображением на память.

Обращение ПУ как ячейке ОЗУ. В памяти резервируется ячейки для ПУ, имеющие регистр адреса, регистр состояния и регистр данных устройства.

№6 слайд

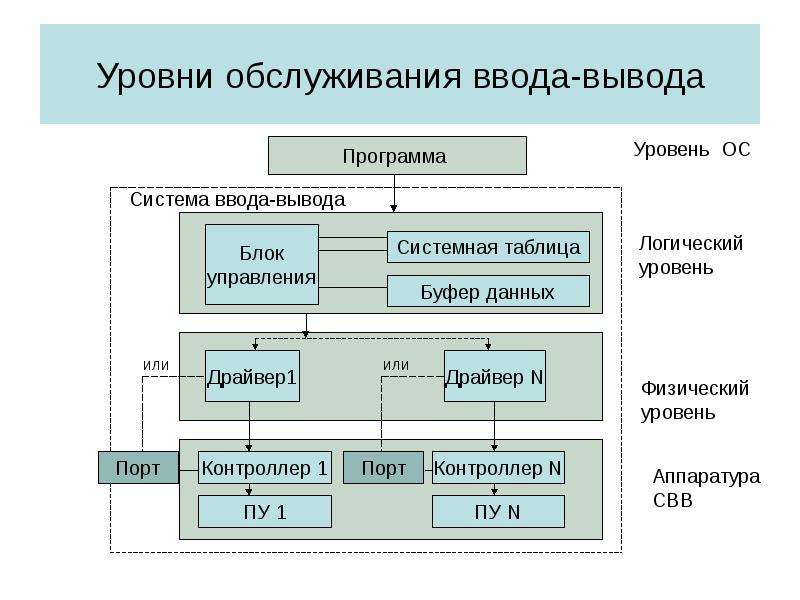

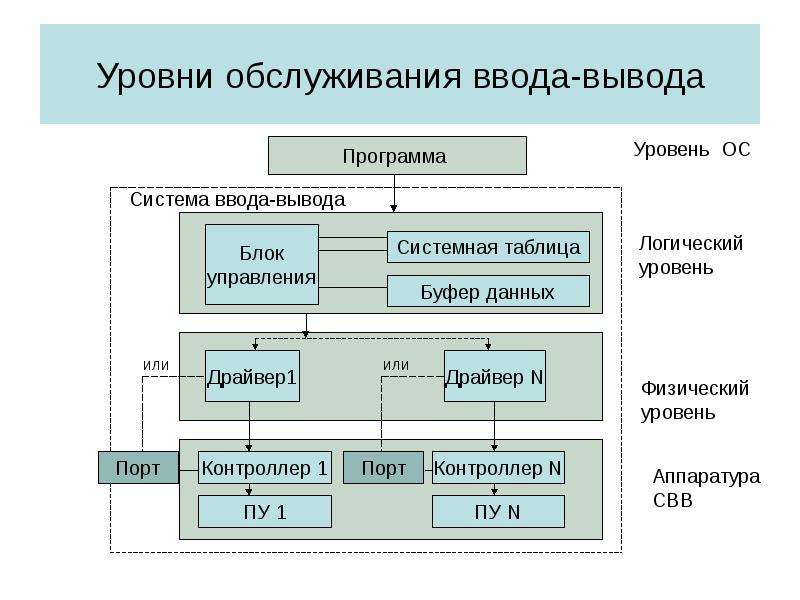

Содержание слайда: Уровни обслуживания ввода-вывода

№7 слайд

Содержание слайда: Функции драйверов

Проверка готовности контроллера и ПУ к обмену;

Формирование управляющих сигналов и данных для ПУ;

Определение действий при обнаружении ошибок;

Формирование сообщения о завершении операции с указанием успешности или неуспешности;

Передача управления на логический уровень.

№8 слайд

Содержание слайда: Способы организации СВВ

Программный.

На основе системы прерываний.

Прямой доступ к памяти.

Коммутаторный.

Без адресный «точка –точка».

Они могут комбинироваться при конкретной реализации системы.

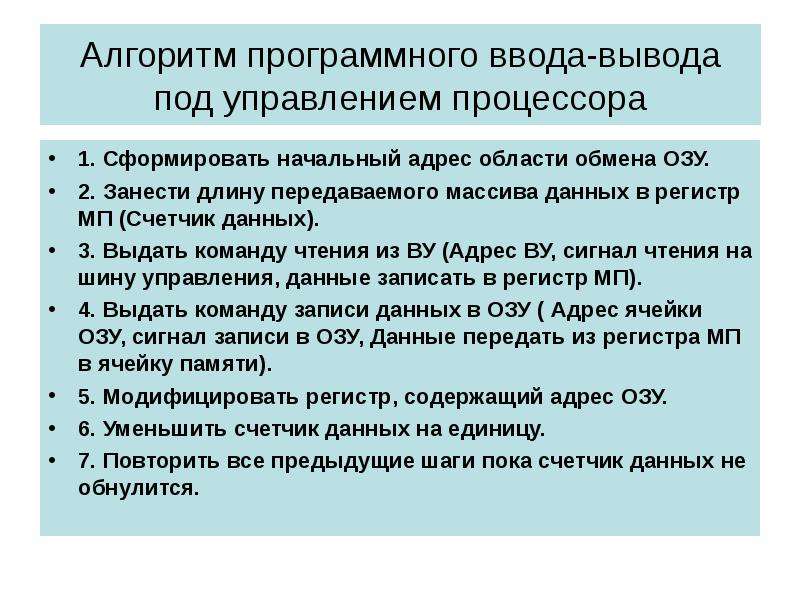

№9 слайд

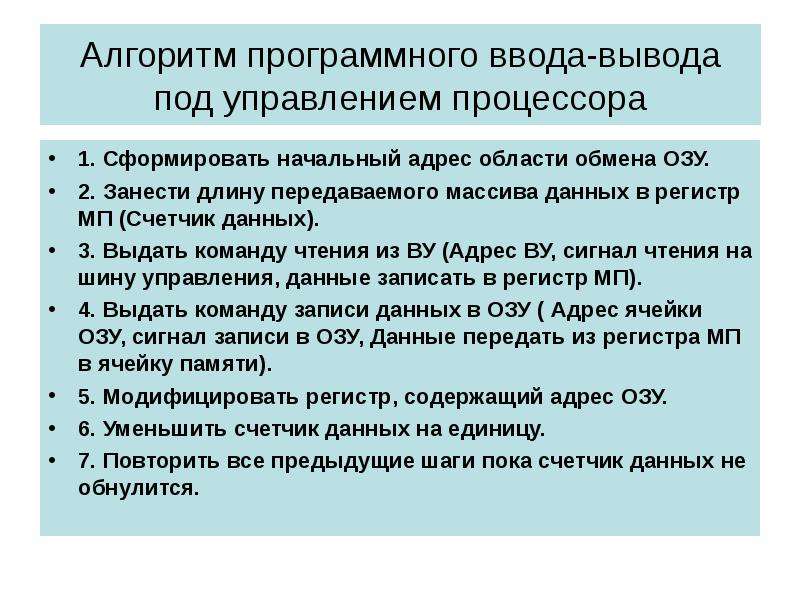

Содержание слайда: Алгоритм программного ввода-вывода под управлением процессора

1. Сформировать начальный адрес области обмена ОЗУ.

2. Занести длину передаваемого массива данных в регистр МП (Счетчик данных).

3. Выдать команду чтения из ВУ (Адрес ВУ, сигнал чтения на шину управления, данные записать в регистр МП).

4. Выдать команду записи данных в ОЗУ ( Адрес ячейки ОЗУ, сигнал записи в ОЗУ, Данные передать из регистра МП в ячейку памяти).

5. Модифицировать регистр, содержащий адрес ОЗУ.

6. Уменьшить счетчик данных на единицу.

7. Повторить все предыдущие шаги пока счетчик данных не обнулится.

№10 слайд

Содержание слайда: Система прерываний

Обработка прерывания.

Организация системы приоритетов через систему арбитража.

№11 слайд

Содержание слайда: Диаграмма прерывания

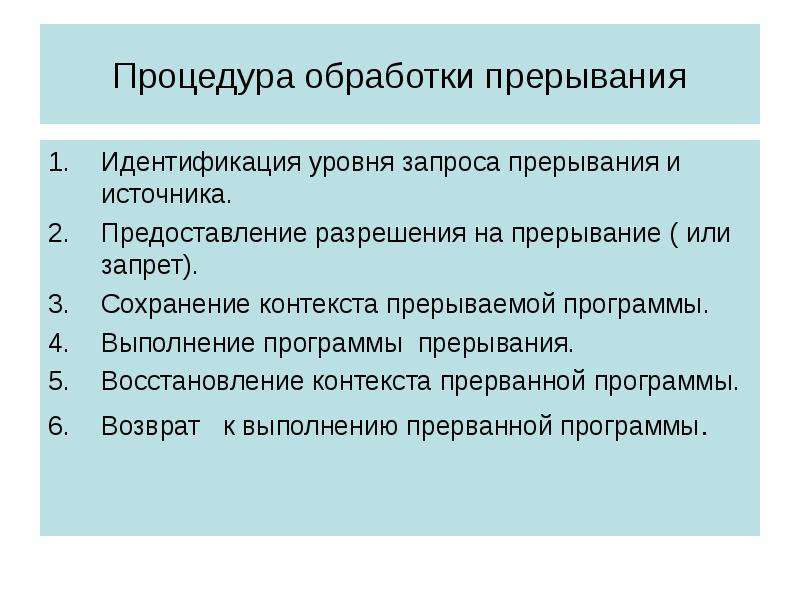

№12 слайд

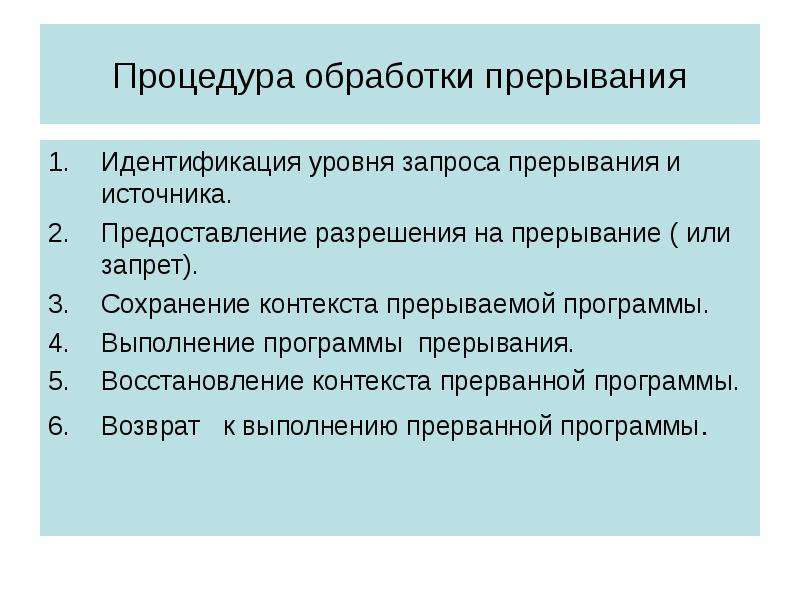

Содержание слайда: Процедура обработки прерывания

Идентификация уровня запроса прерывания и источника.

Предоставление разрешения на прерывание ( или запрет).

Сохранение контекста прерываемой программы.

Выполнение программы прерывания.

Восстановление контекста прерванной программы.

Возврат к выполнению прерванной программы.

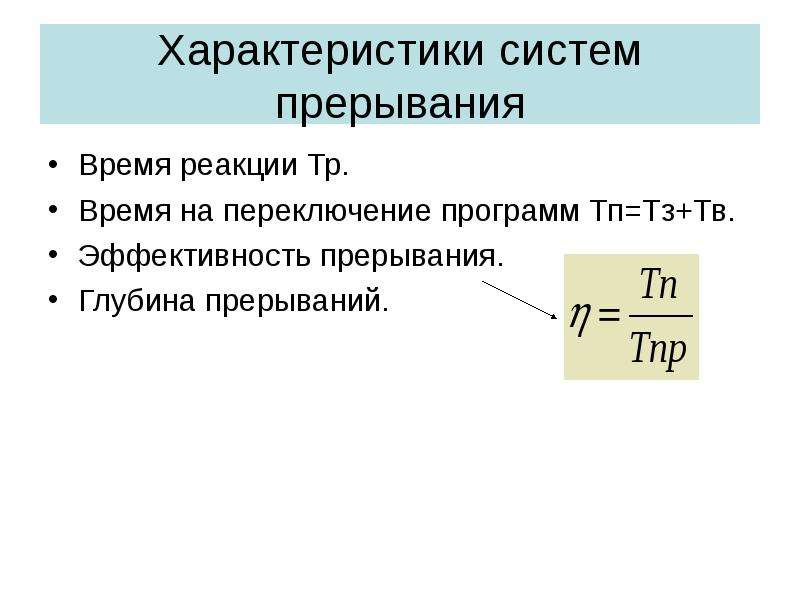

№13 слайд

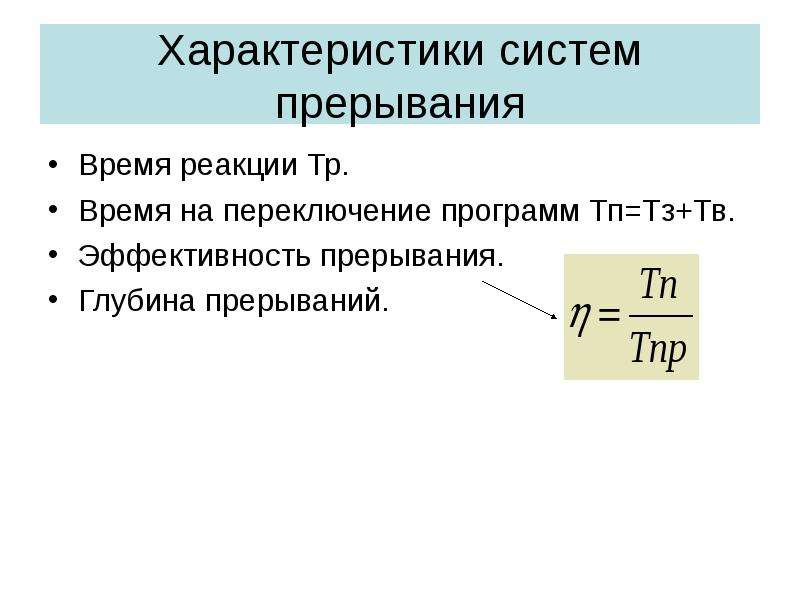

Содержание слайда: Характеристики систем прерывания

Время реакции Тр.

Время на переключение программ Тп=Тз+Тв.

Эффективность прерывания.

Глубина прерываний.

№14 слайд

Содержание слайда: Глубина прерывания

№15 слайд

Содержание слайда: СВВ с использованием системы прерываний

№16 слайд

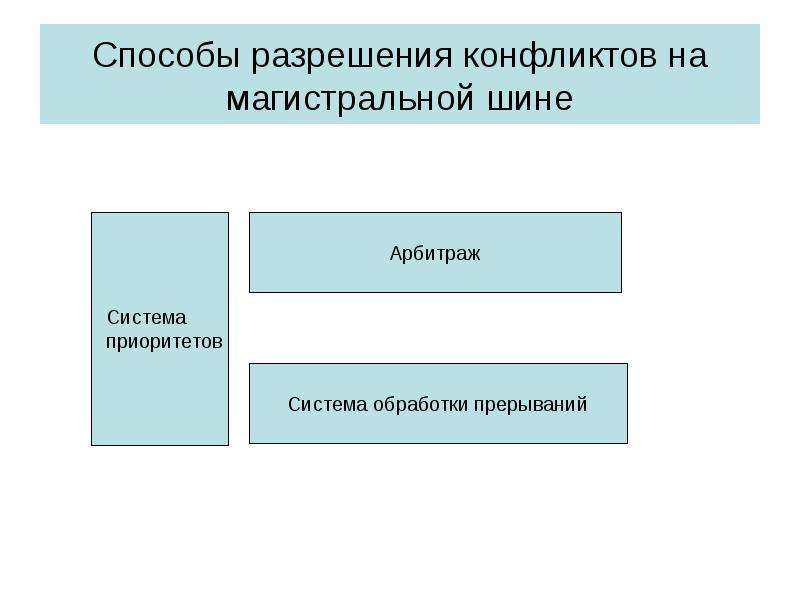

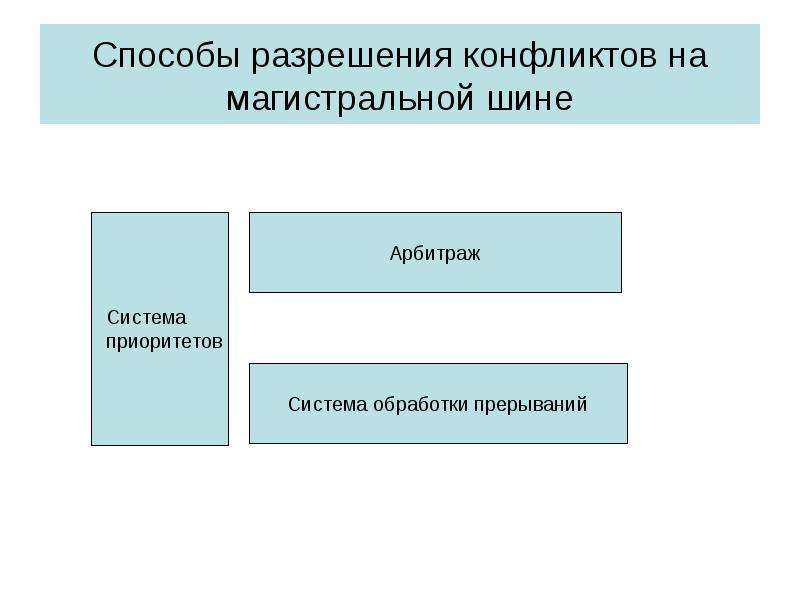

Содержание слайда: Способы разрешения конфликтов на магистральной шине

№17 слайд

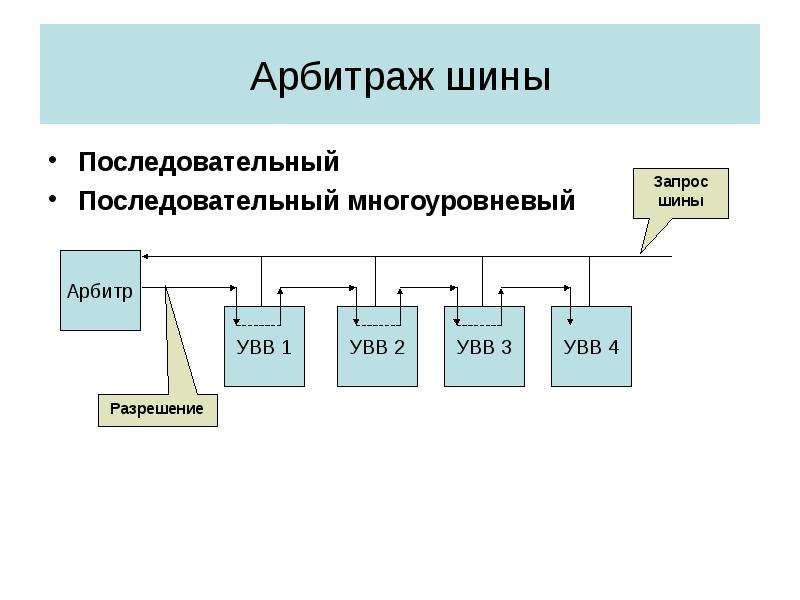

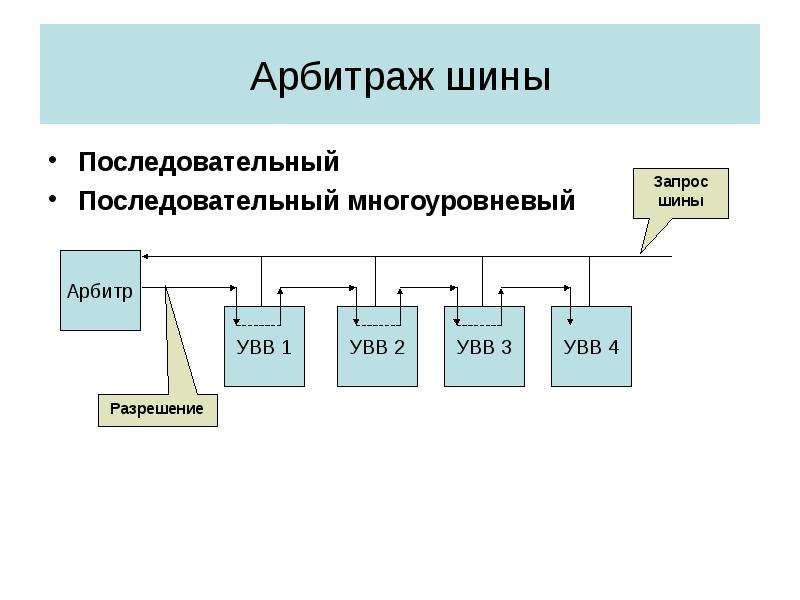

Содержание слайда: Арбитраж шины

Последовательный

Последовательный многоуровневый

№18 слайд

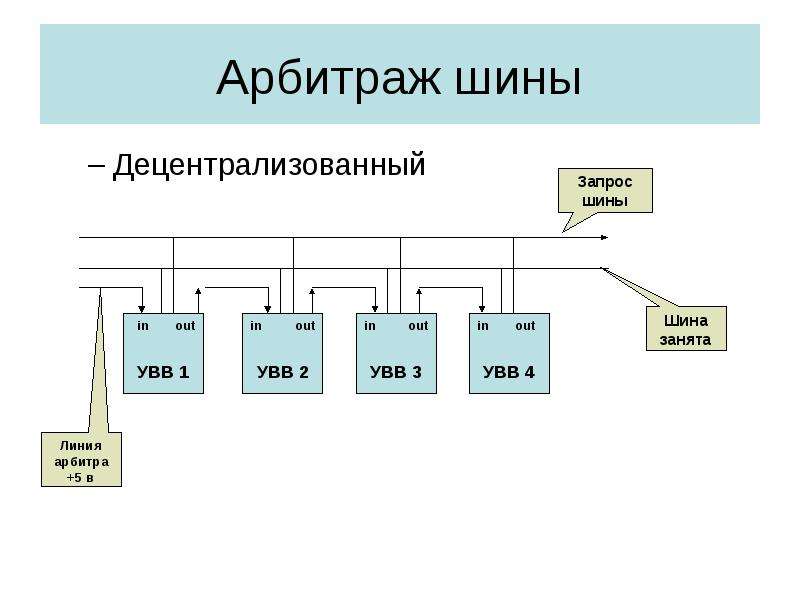

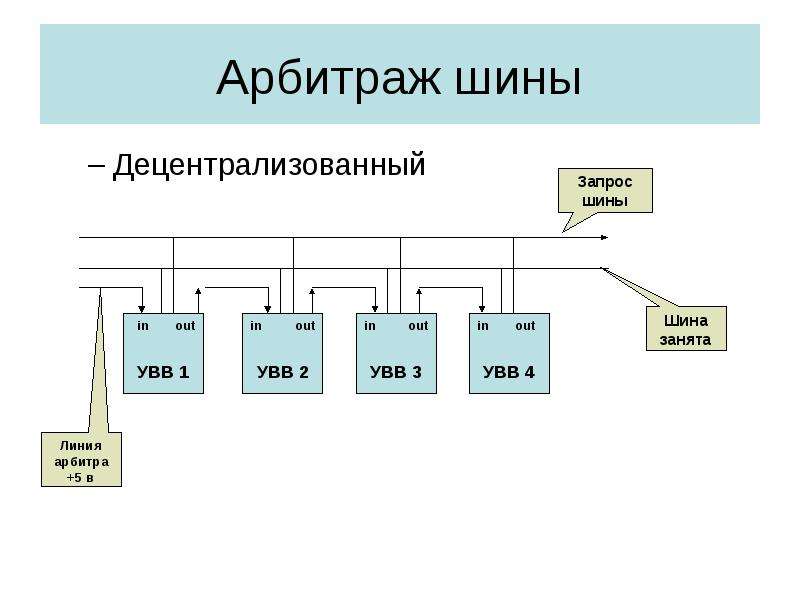

Содержание слайда: Арбитраж шины

Децентрализованный

№19 слайд

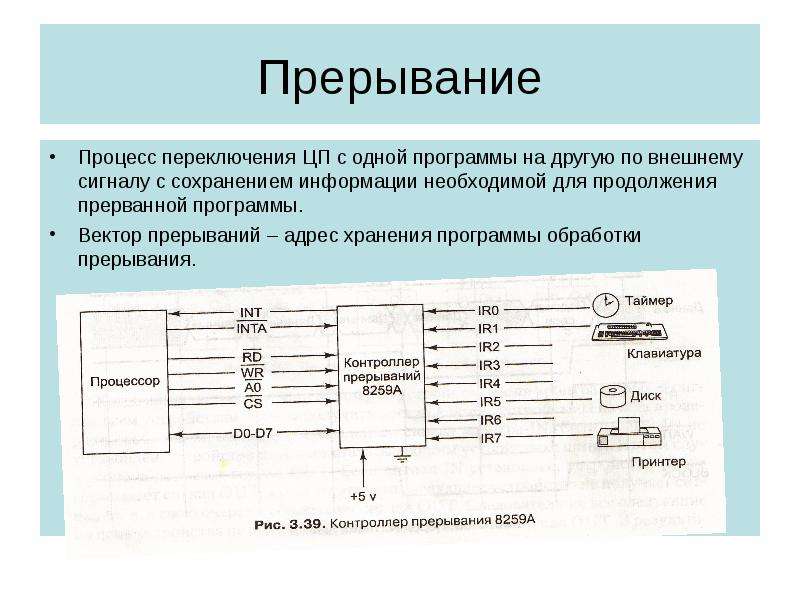

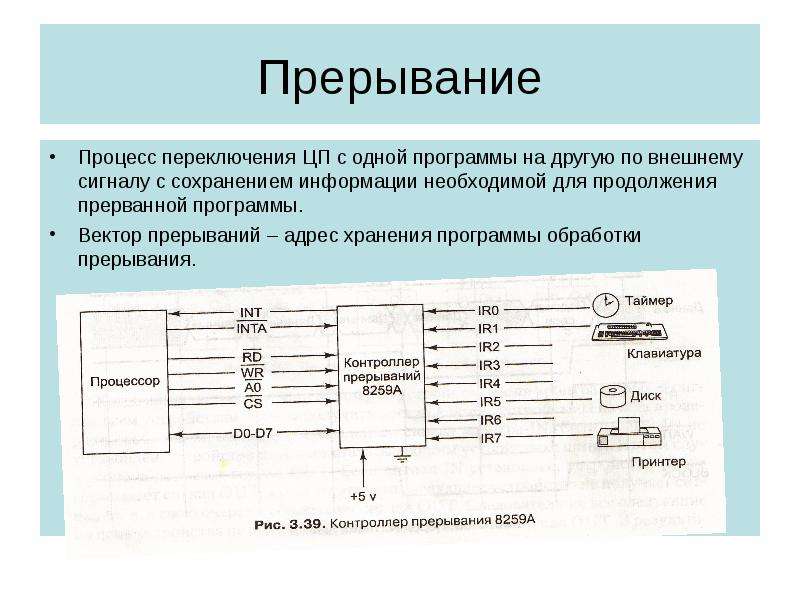

Содержание слайда: Прерывание

Процесс переключения ЦП с одной программы на другую по внешнему сигналу с сохранением информации необходимой для продолжения прерванной программы.

Вектор прерываний – адрес хранения программы обработки прерывания.

№20 слайд

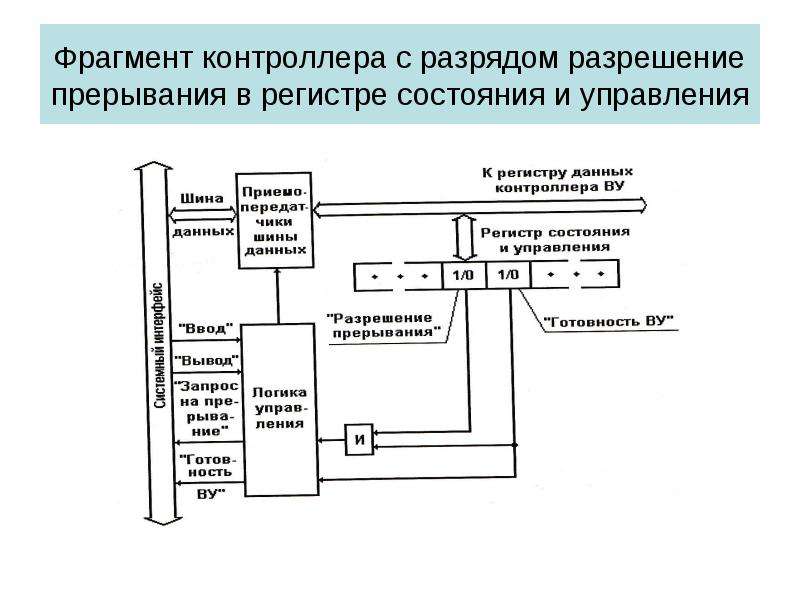

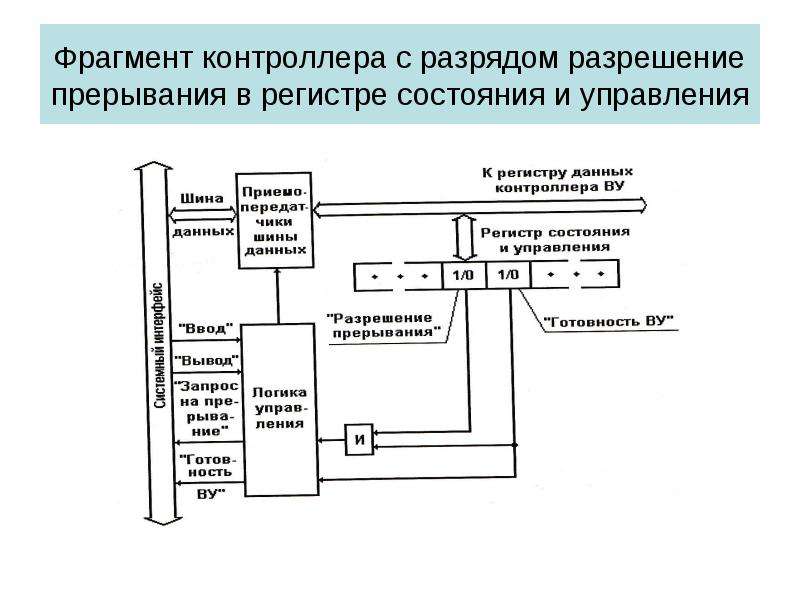

Содержание слайда: Фрагмент контроллера с разрядом разрешение

прерывания в регистре состояния и управления

№21 слайд

Содержание слайда: Вектор прерываний

№22 слайд

Содержание слайда: Контроллер прерываний Intel 8259A

RGI – регистр запросов на прерывание.

PRB – схема арбитр.

ISR - регистр обслуживаемых прерываний.

RGM – регистр маскирования прерываний.

BU – схема управления.

BD – буфер данных выдает на шину вектор прерывания.

CMP – схема организации каскада.

RWBU – блок управления записью, чтением.

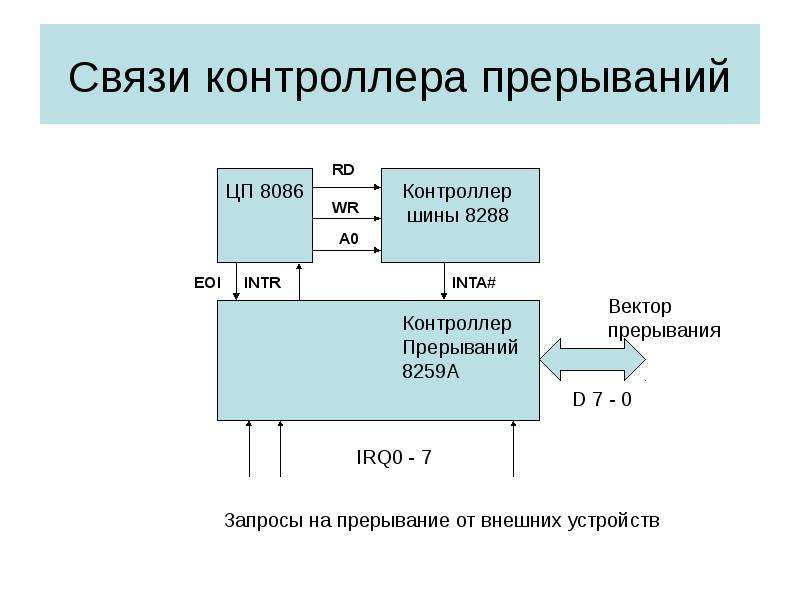

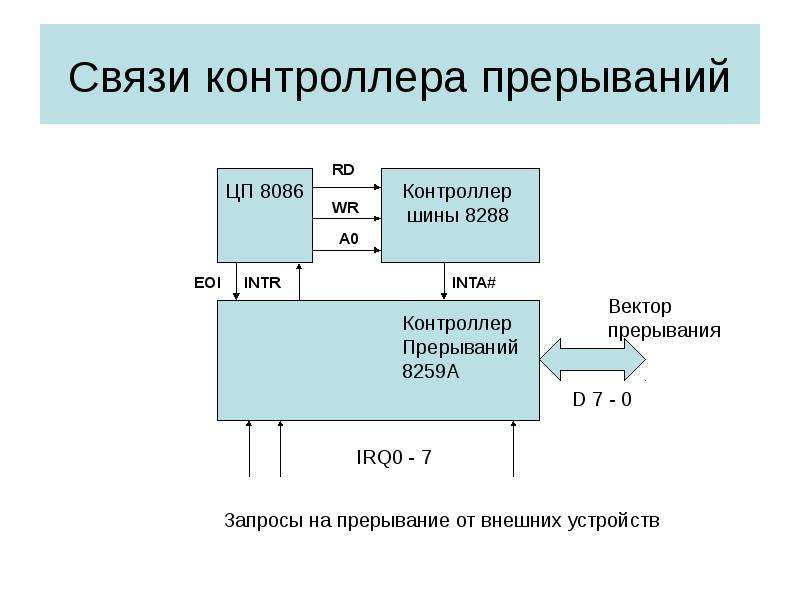

№23 слайд

Содержание слайда: Связи контроллера прерываний

№24 слайд

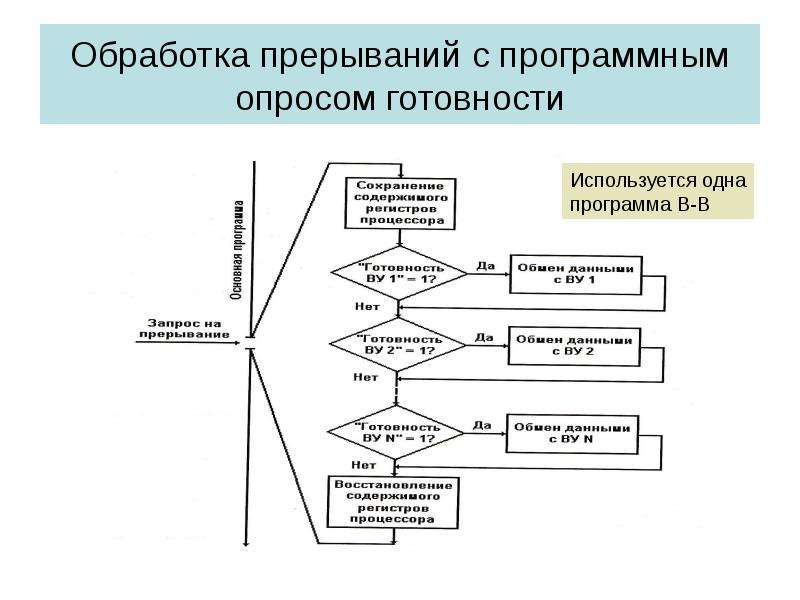

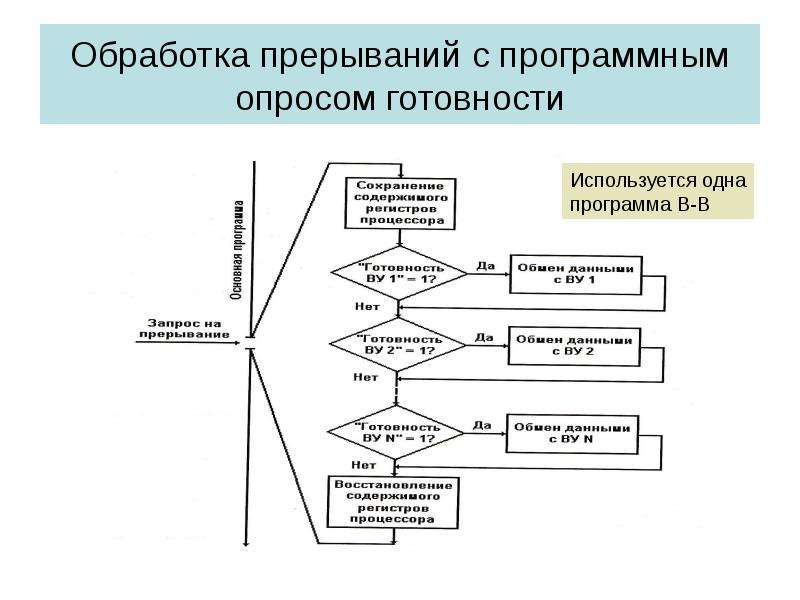

Содержание слайда: Обработка прерываний с программным опросом готовности

№25 слайд

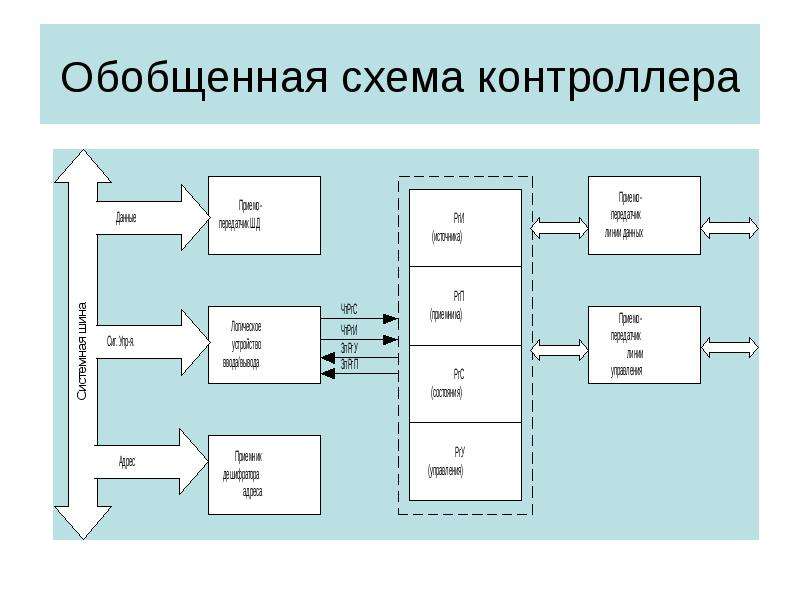

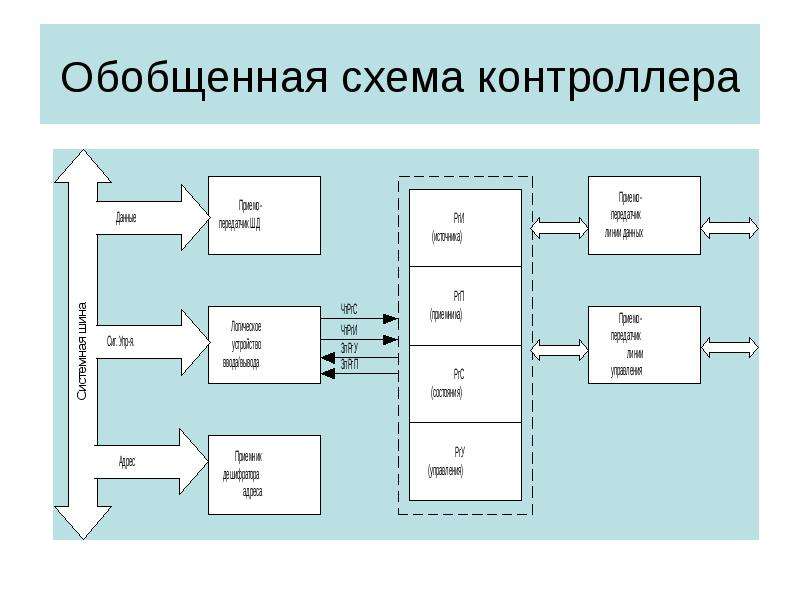

Содержание слайда: Обобщенная схема контроллера

№26 слайд

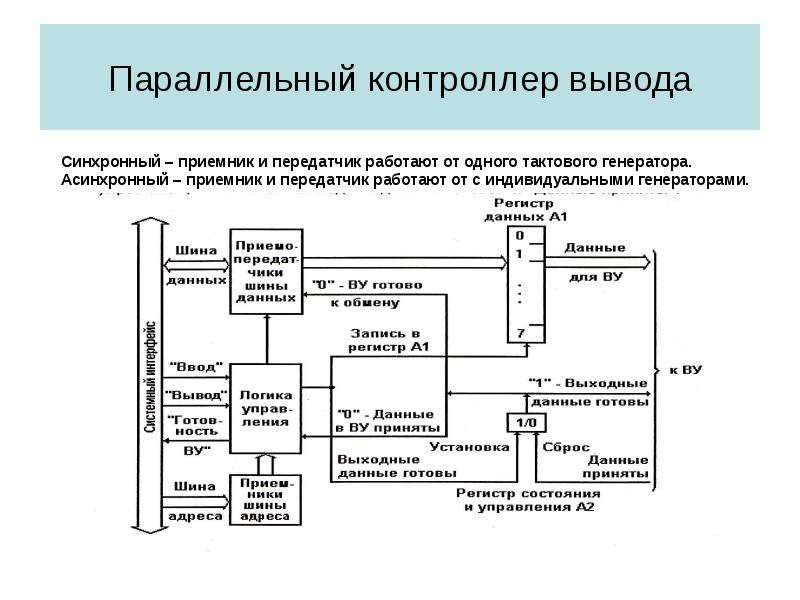

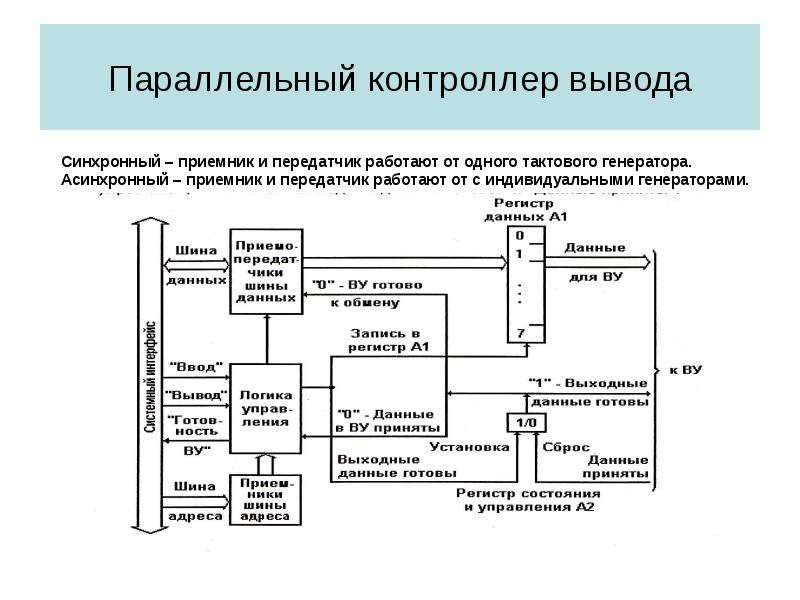

Содержание слайда: Параллельный контроллер вывода

№27 слайд

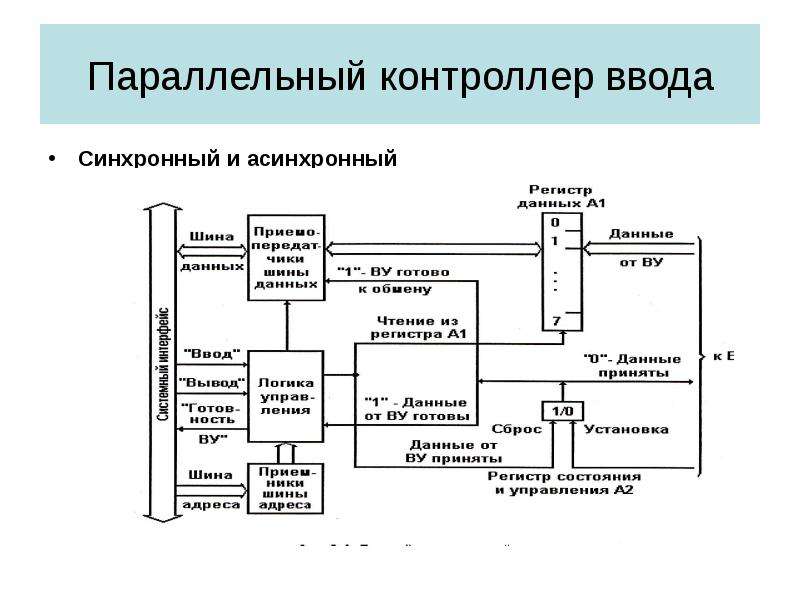

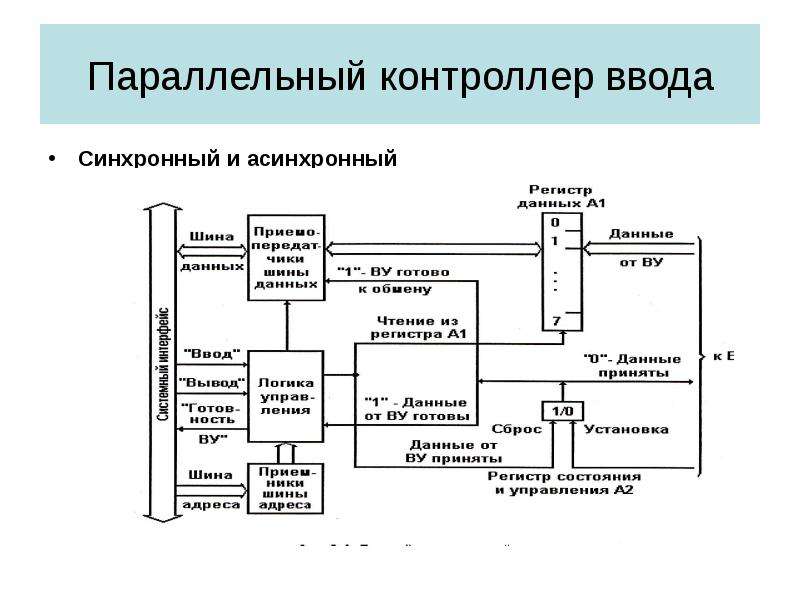

Содержание слайда: Параллельный контроллер ввода

Синхронный и асинхронный

№28 слайд

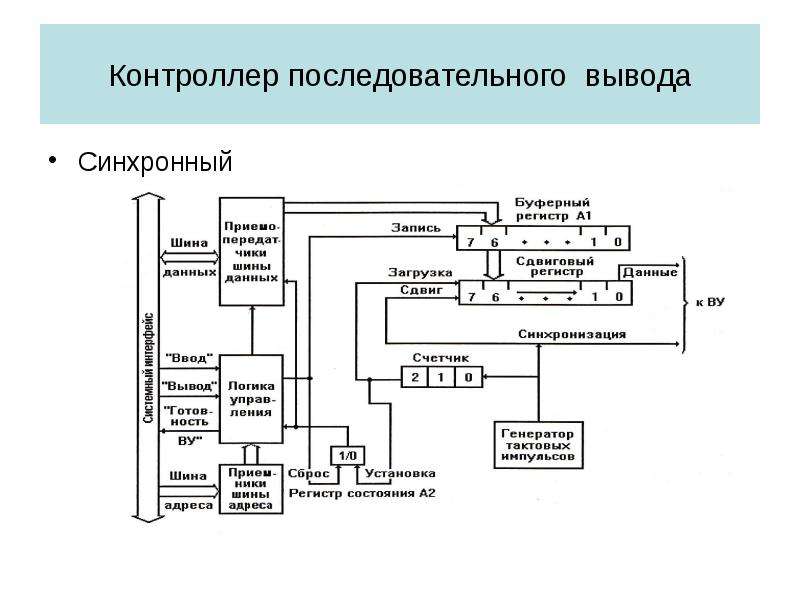

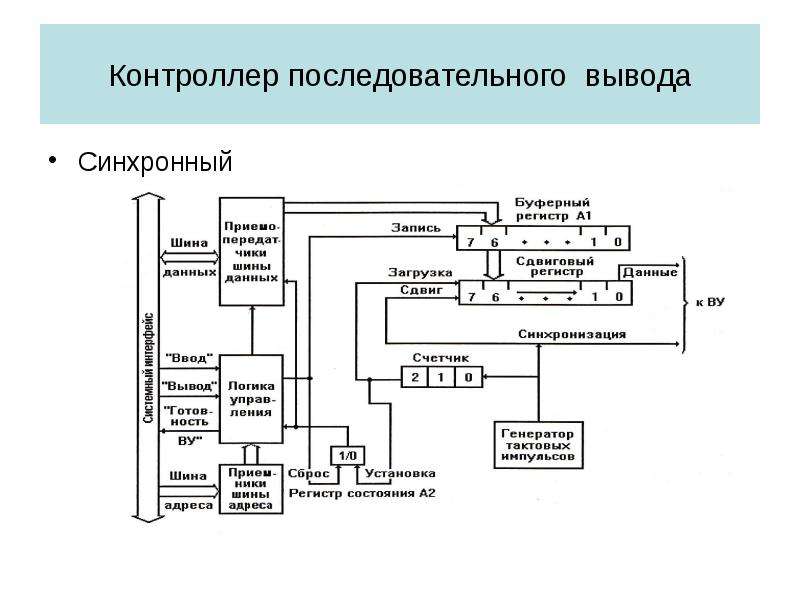

Содержание слайда: Контроллер последовательного вывода

Синхронный

№29 слайд

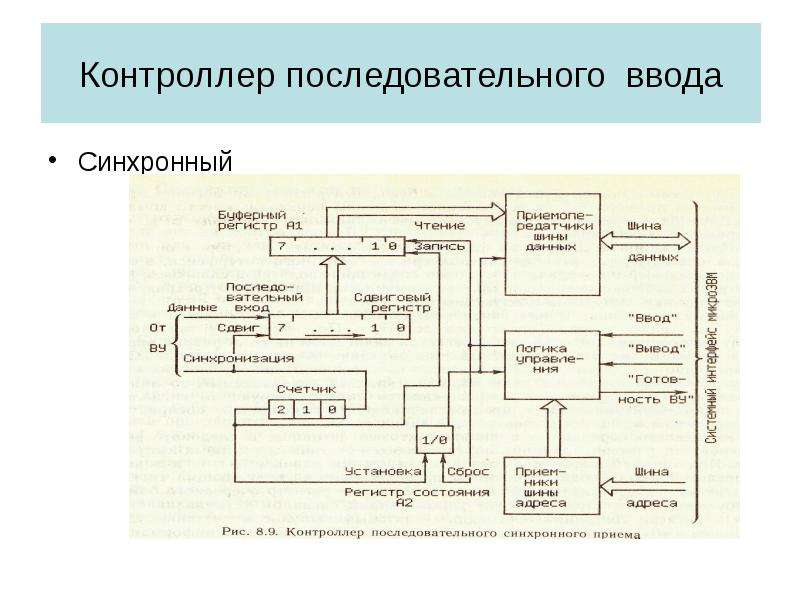

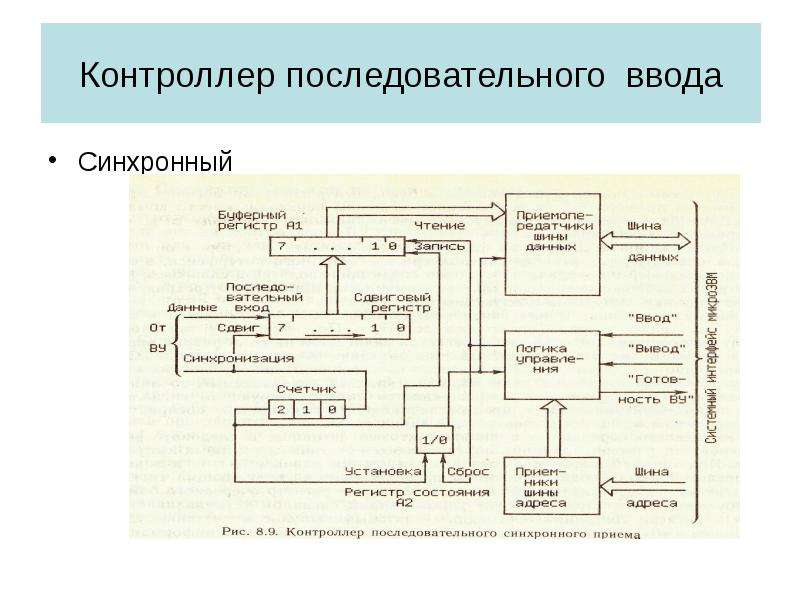

Содержание слайда: Контроллер последовательного ввода

Синхронный

№30 слайд

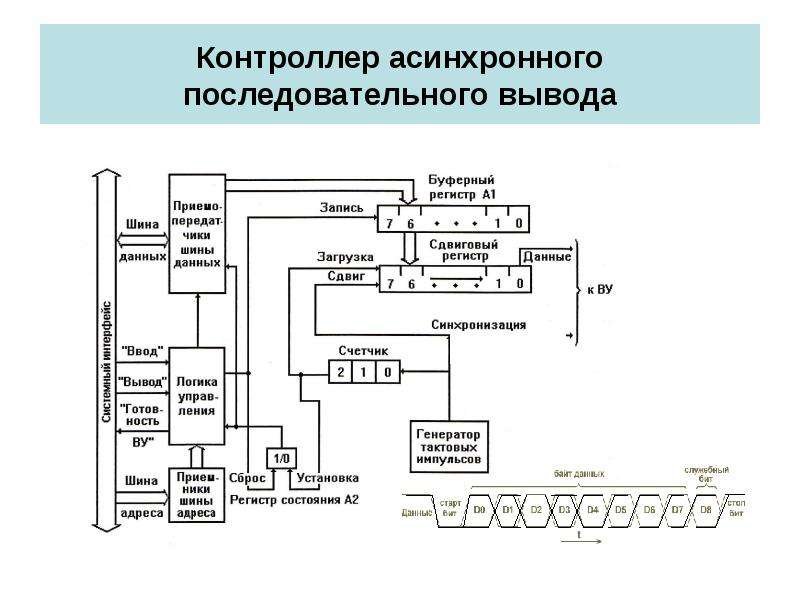

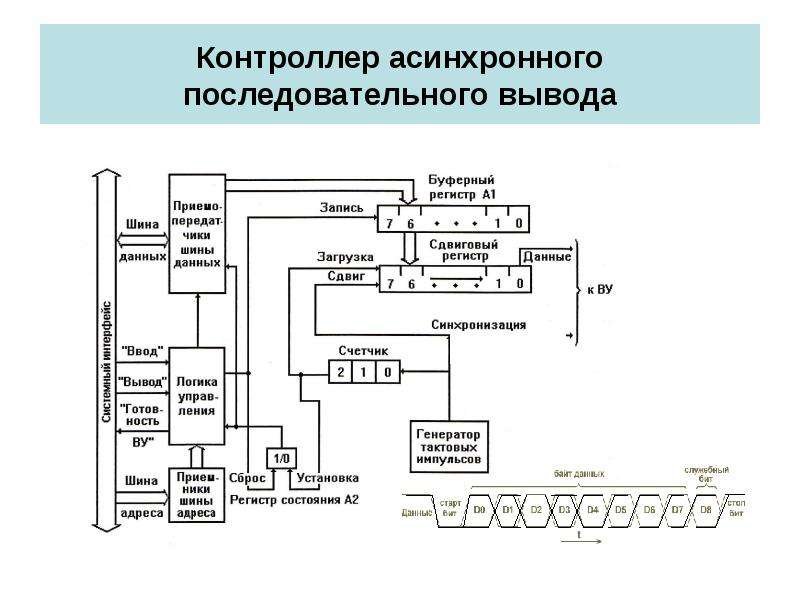

Содержание слайда: Контроллер асинхронного последовательного вывода

№31 слайд

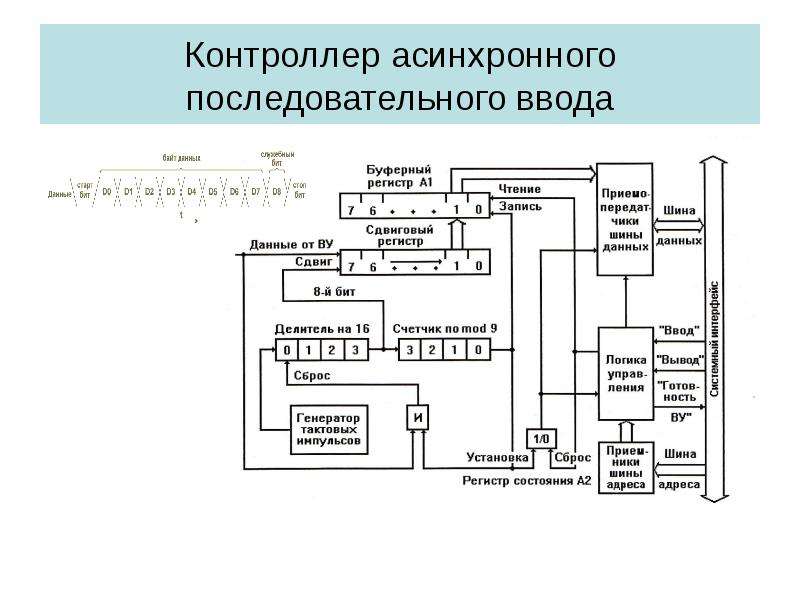

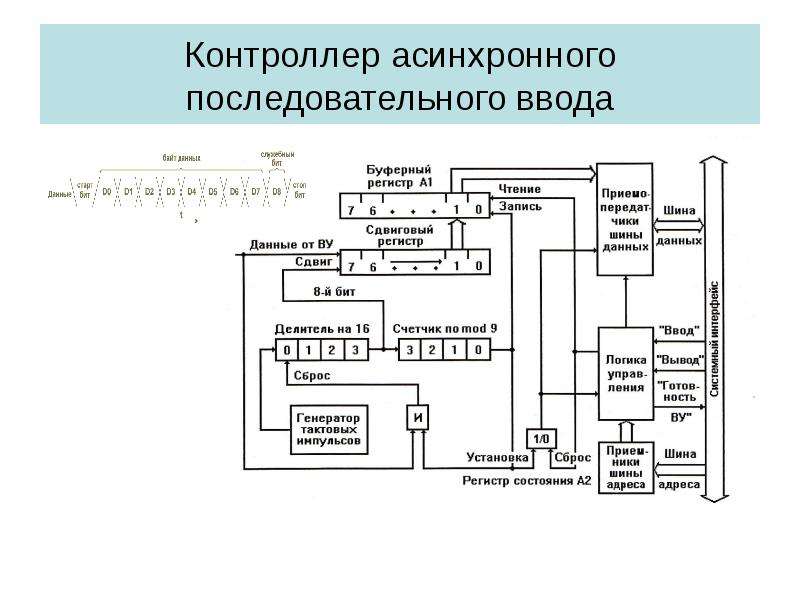

Содержание слайда: Контроллер асинхронного последовательного ввода

№32 слайд

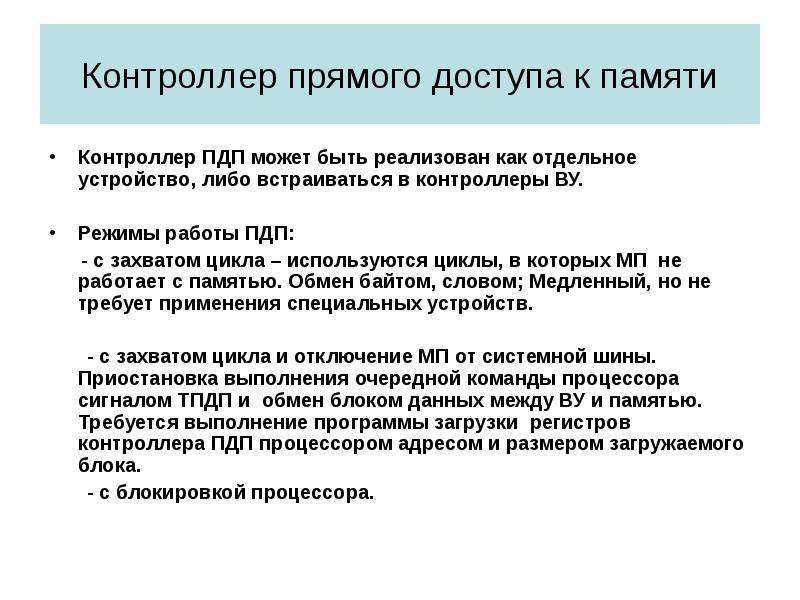

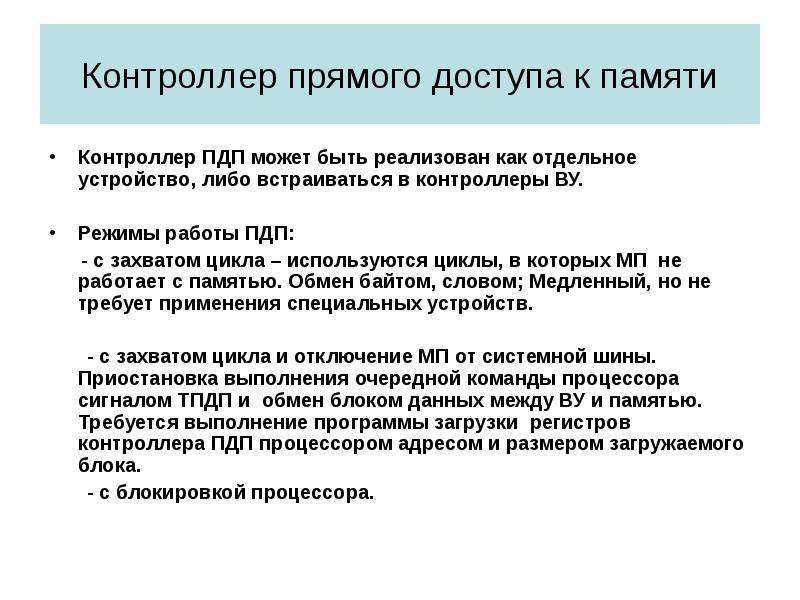

Содержание слайда: Контроллер прямого доступа к памяти

Контроллер ПДП может быть реализован как отдельное устройство, либо встраиваться в контроллеры ВУ.

Режимы работы ПДП:

- с захватом цикла – используются циклы, в которых МП не работает с памятью. Обмен байтом, словом; Медленный, но не требует применения специальных устройств.

- с захватом цикла и отключение МП от системной шины. Приостановка выполнения очередной команды процессора сигналом ТПДП и обмен блоком данных между ВУ и памятью. Требуется выполнение программы загрузки регистров контроллера ПДП процессором адресом и размером загружаемого блока.

- с блокировкой процессора.

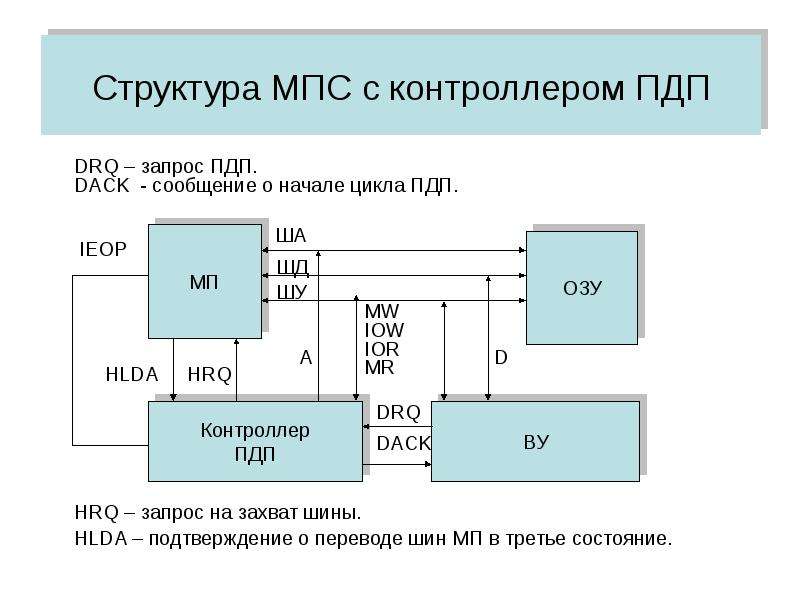

№33 слайд

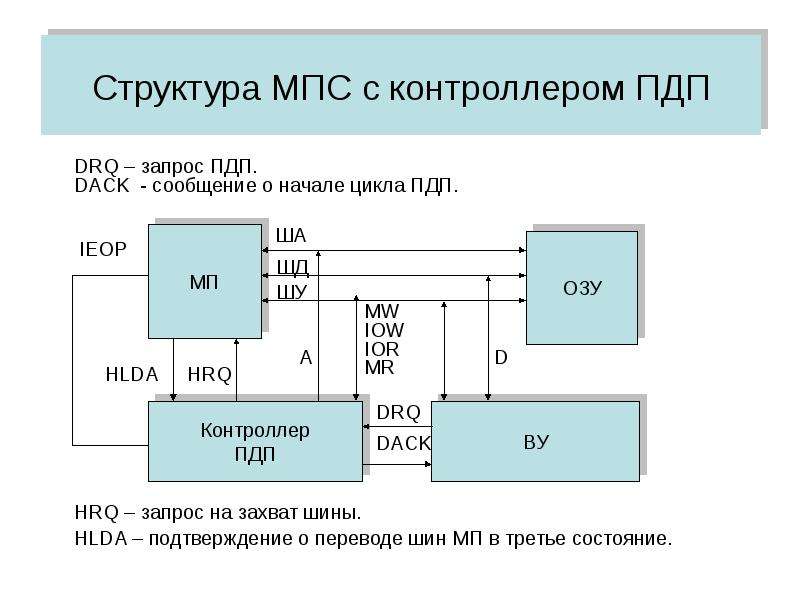

Содержание слайда: Структура МПС с контроллером ПДП

№34 слайд

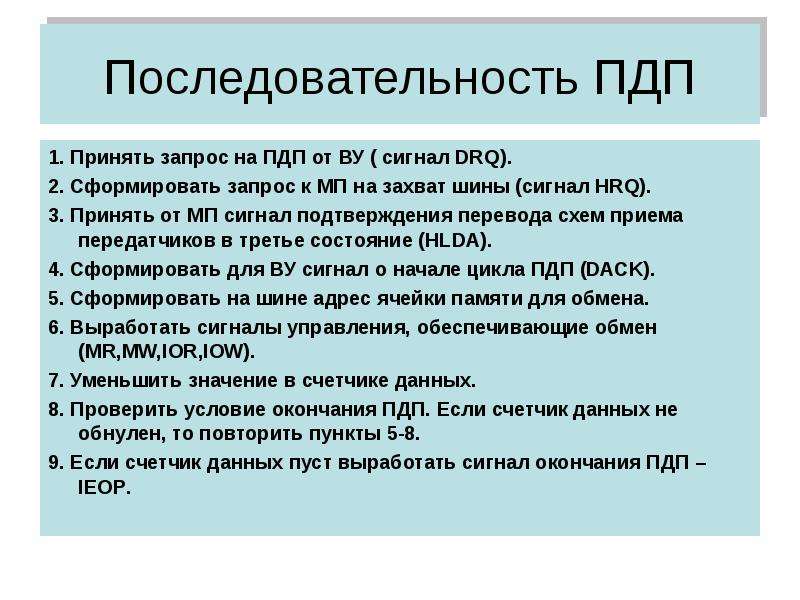

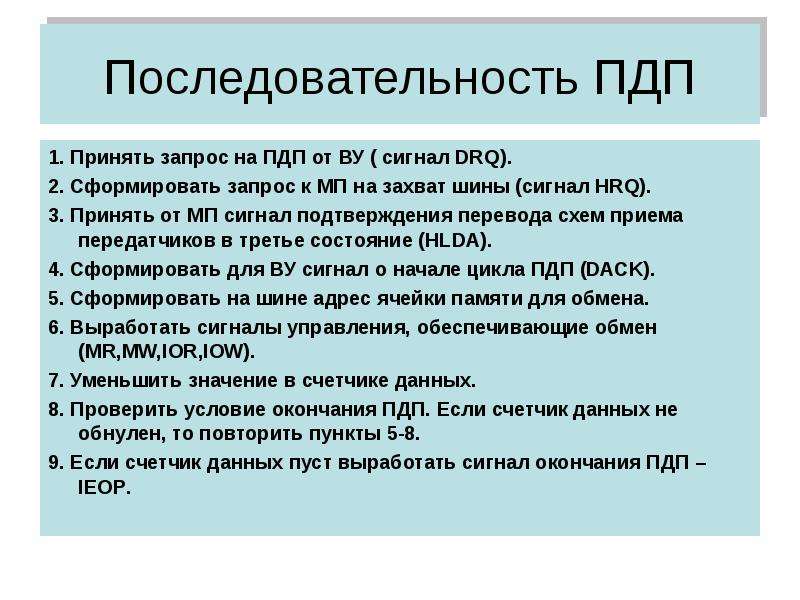

Содержание слайда: Последовательность ПДП

1. Принять запрос на ПДП от ВУ ( сигнал DRQ).

2. Сформировать запрос к МП на захват шины (сигнал HRQ).

3. Принять от МП сигнал подтверждения перевода схем приема передатчиков в третье состояние (HLDA).

4. Сформировать для ВУ сигнал о начале цикла ПДП (DACK).

5. Сформировать на шине адрес ячейки памяти для обмена.

6. Выработать сигналы управления, обеспечивающие обмен (MR,MW,IOR,IOW).

7. Уменьшить значение в счетчике данных.

8. Проверить условие окончания ПДП. Если счетчик данных не обнулен, то повторить пункты 5-8.

9. Если счетчик данных пуст выработать сигнал окончания ПДП – IEOP.

№35 слайд

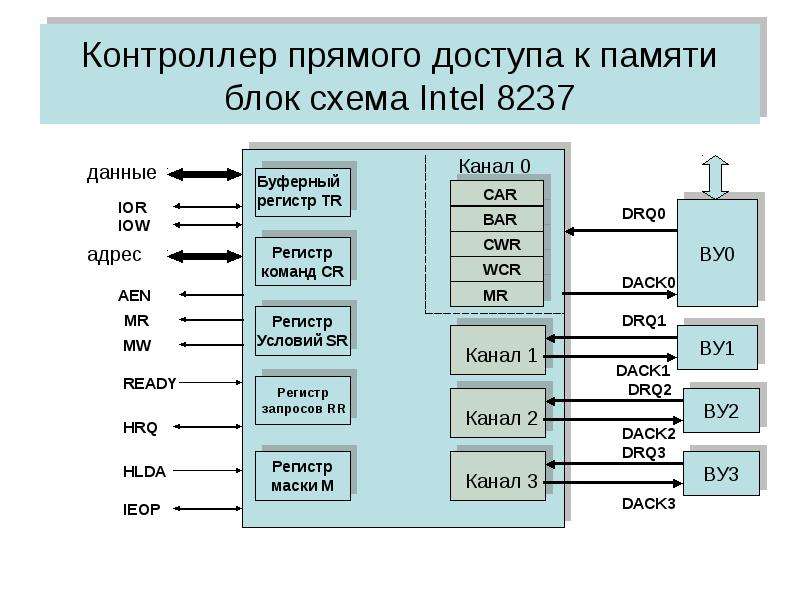

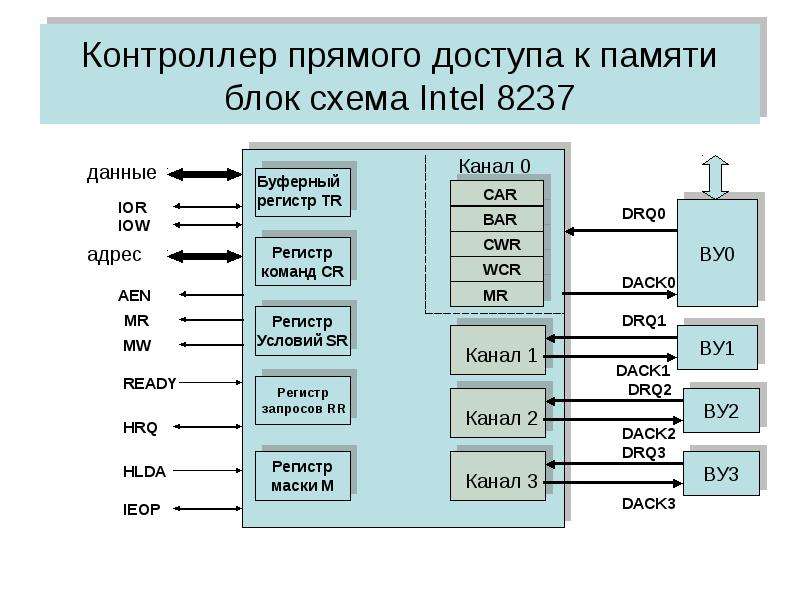

Содержание слайда: Контроллер прямого доступа к памяти

блок схема Intel 8237

№36 слайд

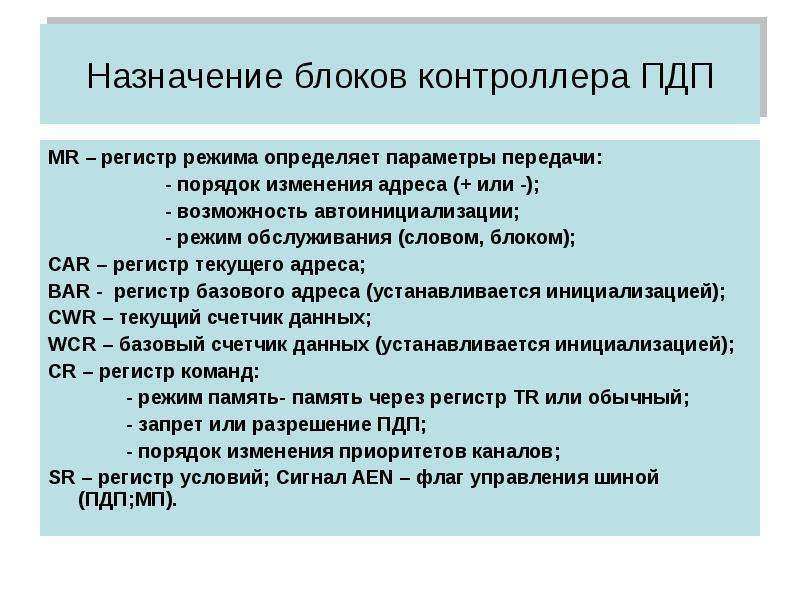

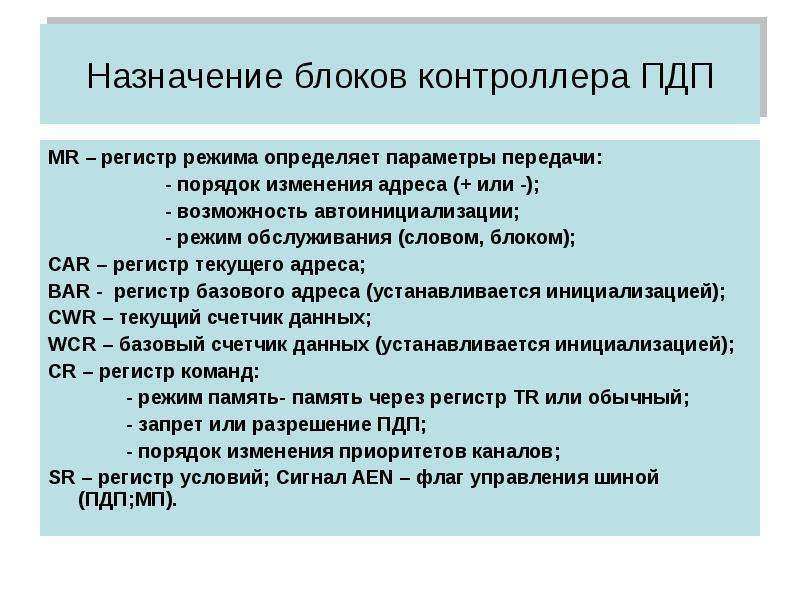

Содержание слайда: Назначение блоков контроллера ПДП

MR – регистр режима определяет параметры передачи:

- порядок изменения адреса (+ или -);

- возможность автоинициализации;

- режим обслуживания (словом, блоком);

CAR – регистр текущего адреса;

BAR - регистр базового адреса (устанавливается инициализацией);

CWR – текущий счетчик данных;

WCR – базовый счетчик данных (устанавливается инициализацией);

CR – регистр команд:

- режим память- память через регистр TR или обычный;

- запрет или разрешение ПДП;

- порядок изменения приоритетов каналов;

SR – регистр условий; Сигнал AEN – флаг управления шиной (ПДП;МП).

№37 слайд

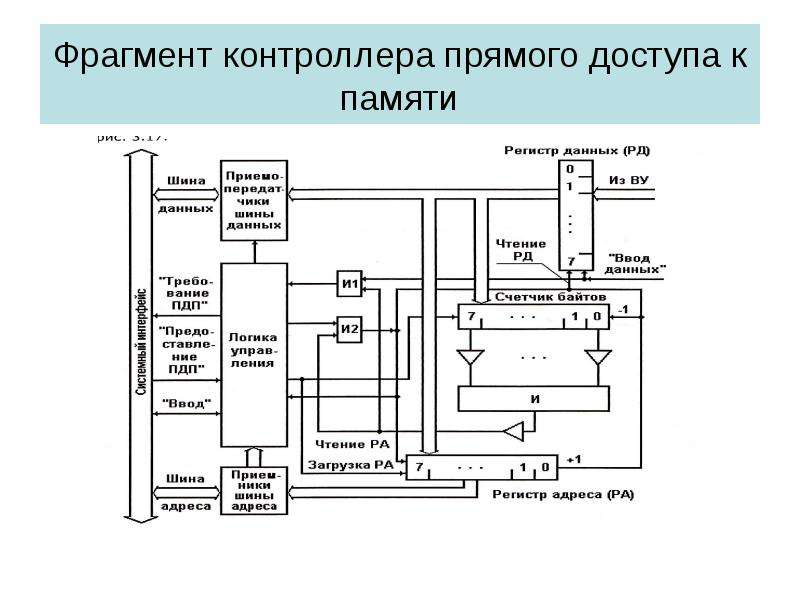

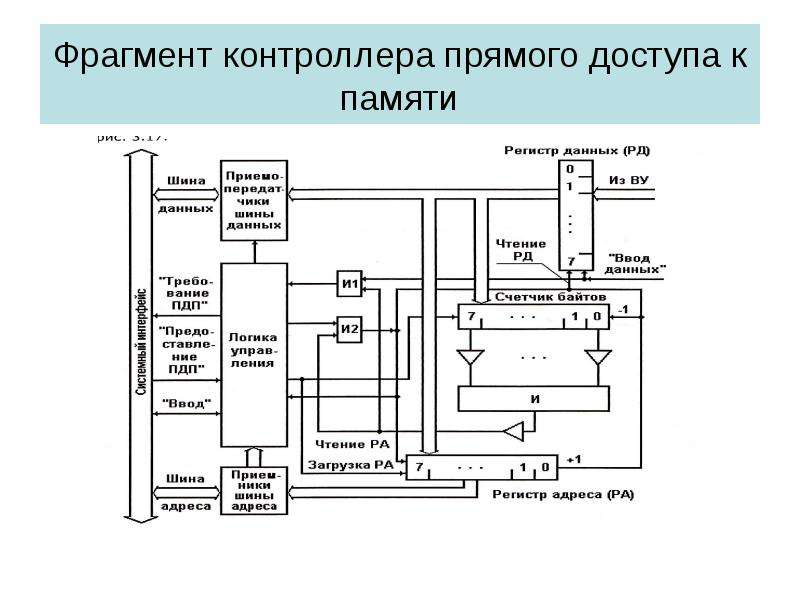

Содержание слайда: Фрагмент контроллера прямого доступа к памяти

№38 слайд

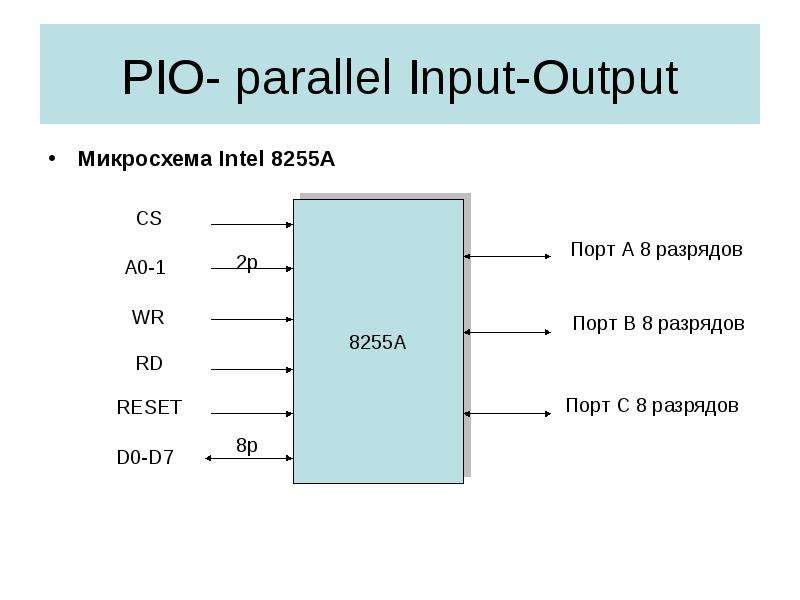

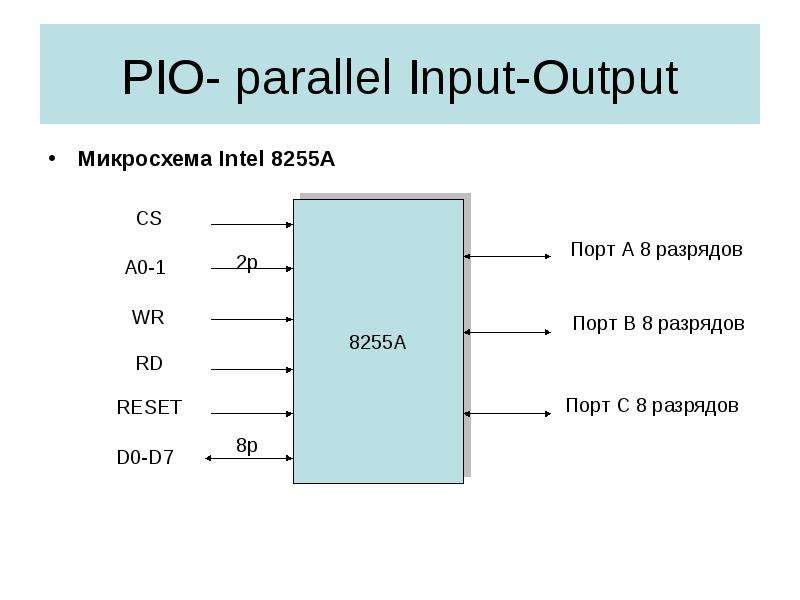

Содержание слайда: PIO- parallel Input-Output

Микросхема Intel 8255A

№39 слайд

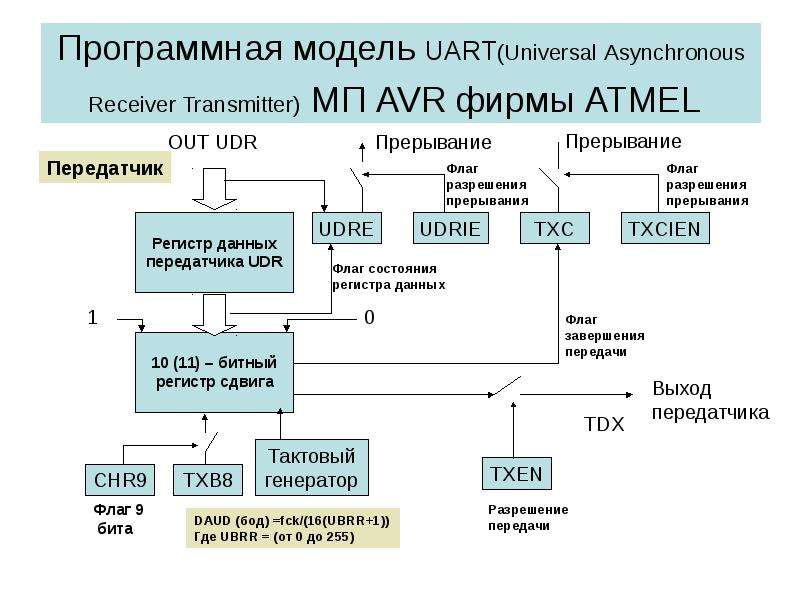

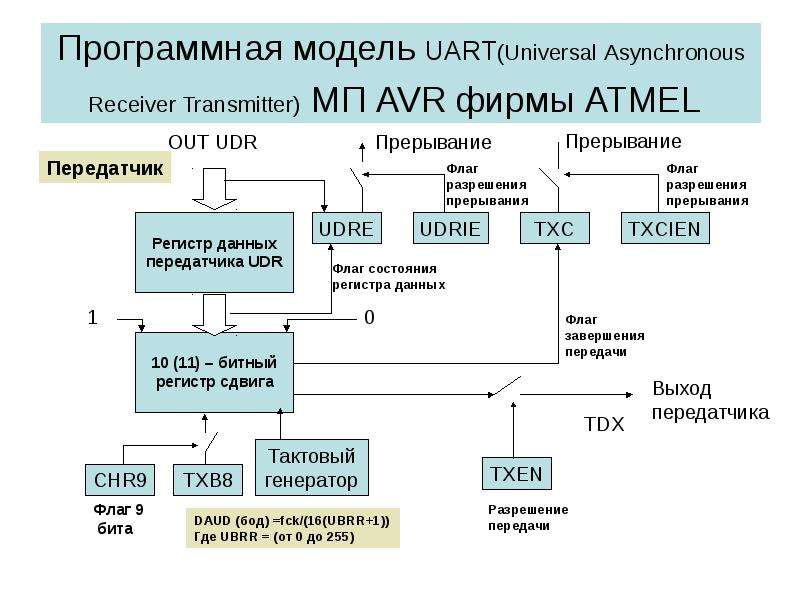

Содержание слайда: Программная модель UART(Universal Asynchronous Receiver Transmitter) МП AVR фирмы ATMEL

№40 слайд

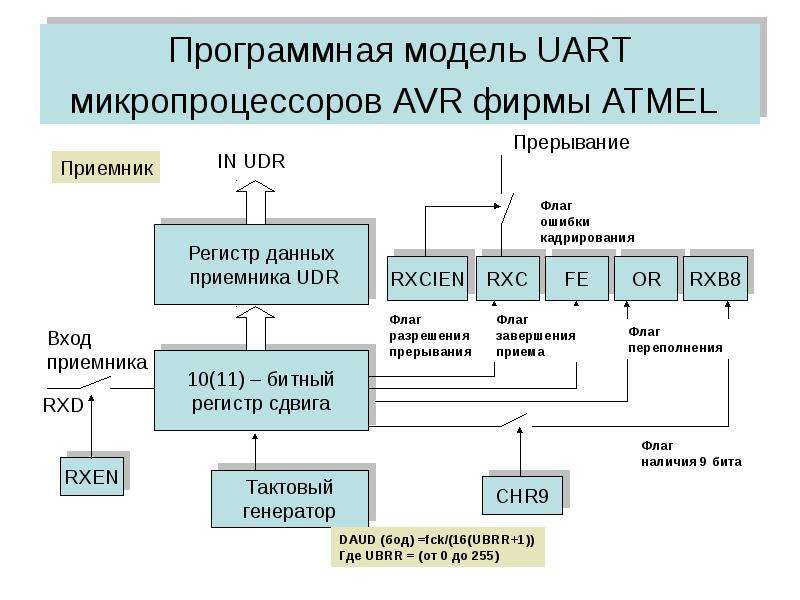

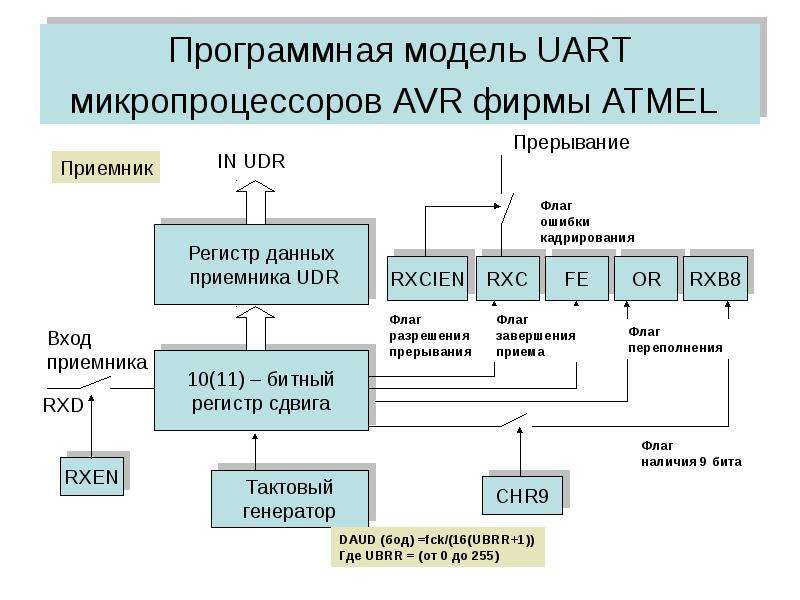

Содержание слайда: Программная модель UART микропроцессоров AVR фирмы ATMEL

№41 слайд

№42 слайд

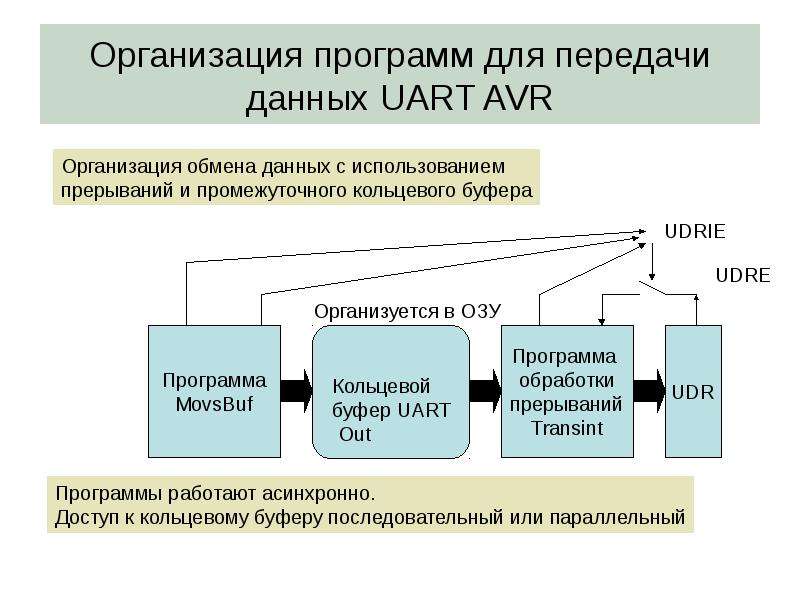

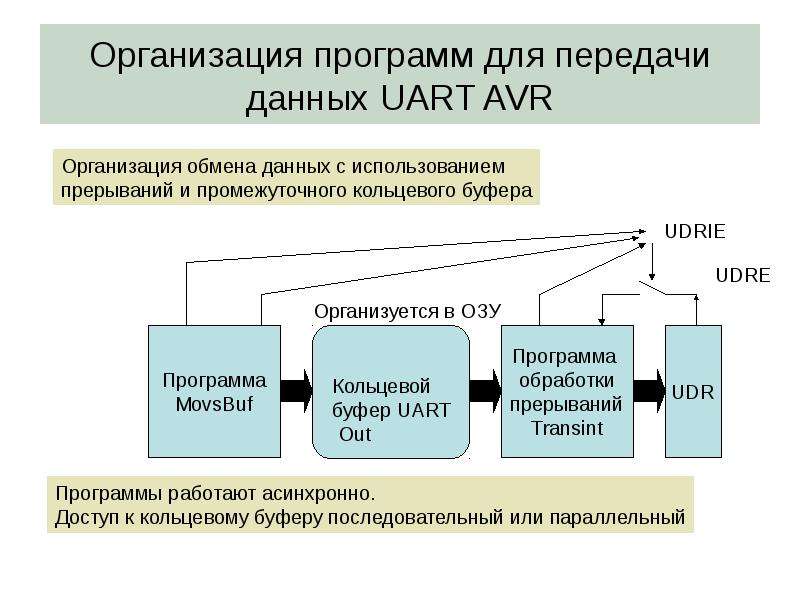

Содержание слайда: Организация программ для передачи данных UART AVR

№43 слайд

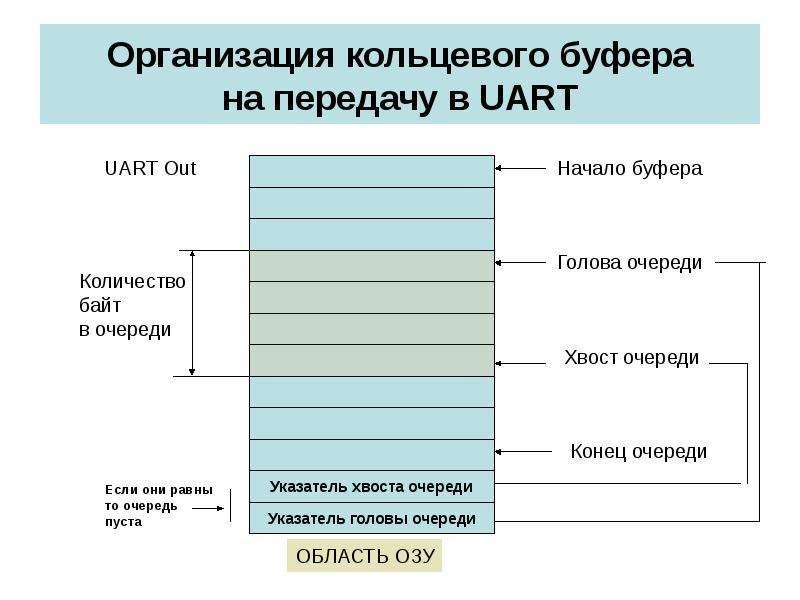

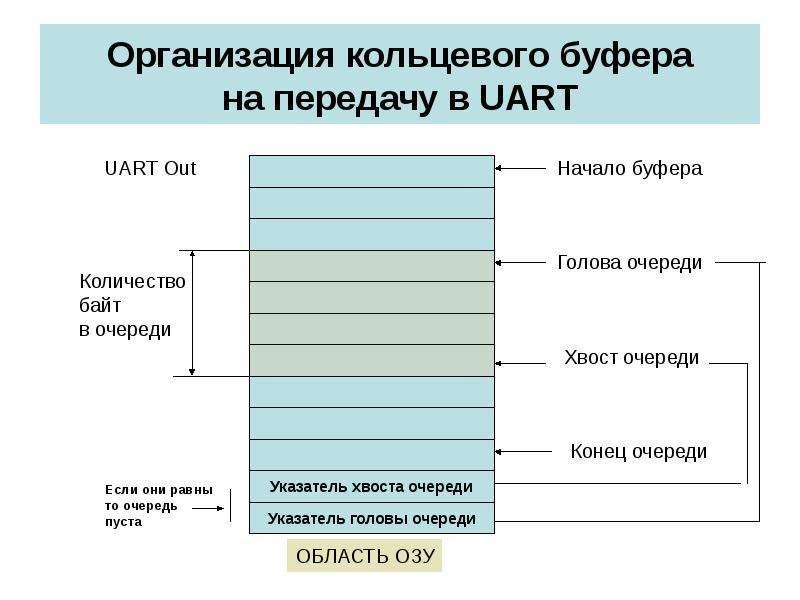

Содержание слайда: Организация кольцевого буфера

на передачу в UART

№44 слайд

Содержание слайда: Организация программ для приема данных UART AVR

№45 слайд

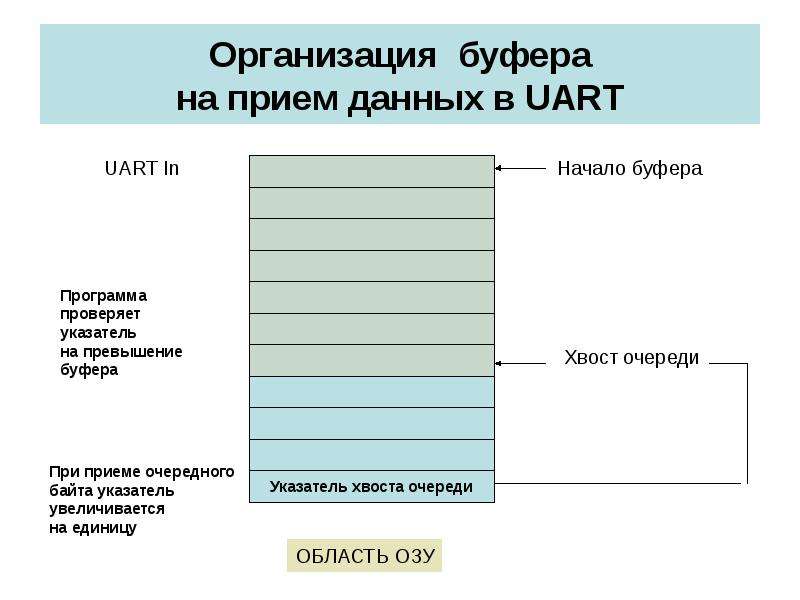

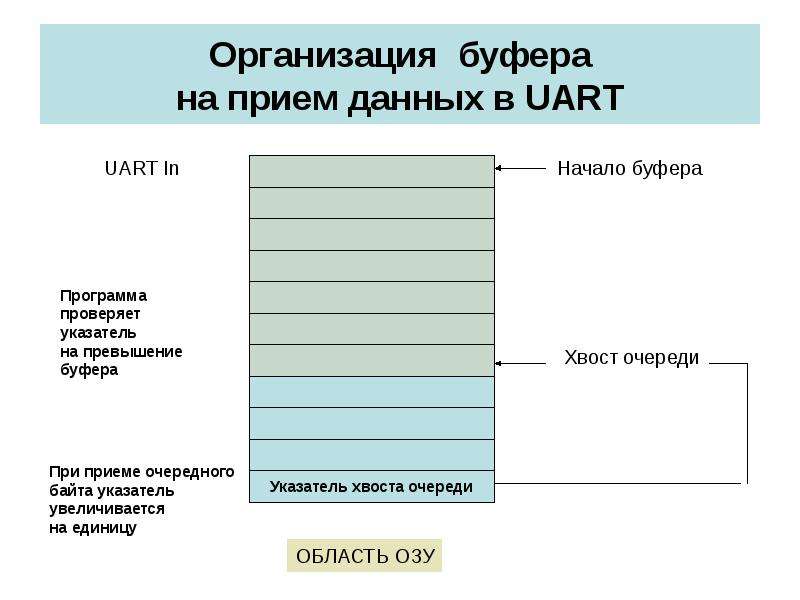

Содержание слайда: Организация буфера

на прием данных в UART